LabVIEW FPGA, 2015 compilation error

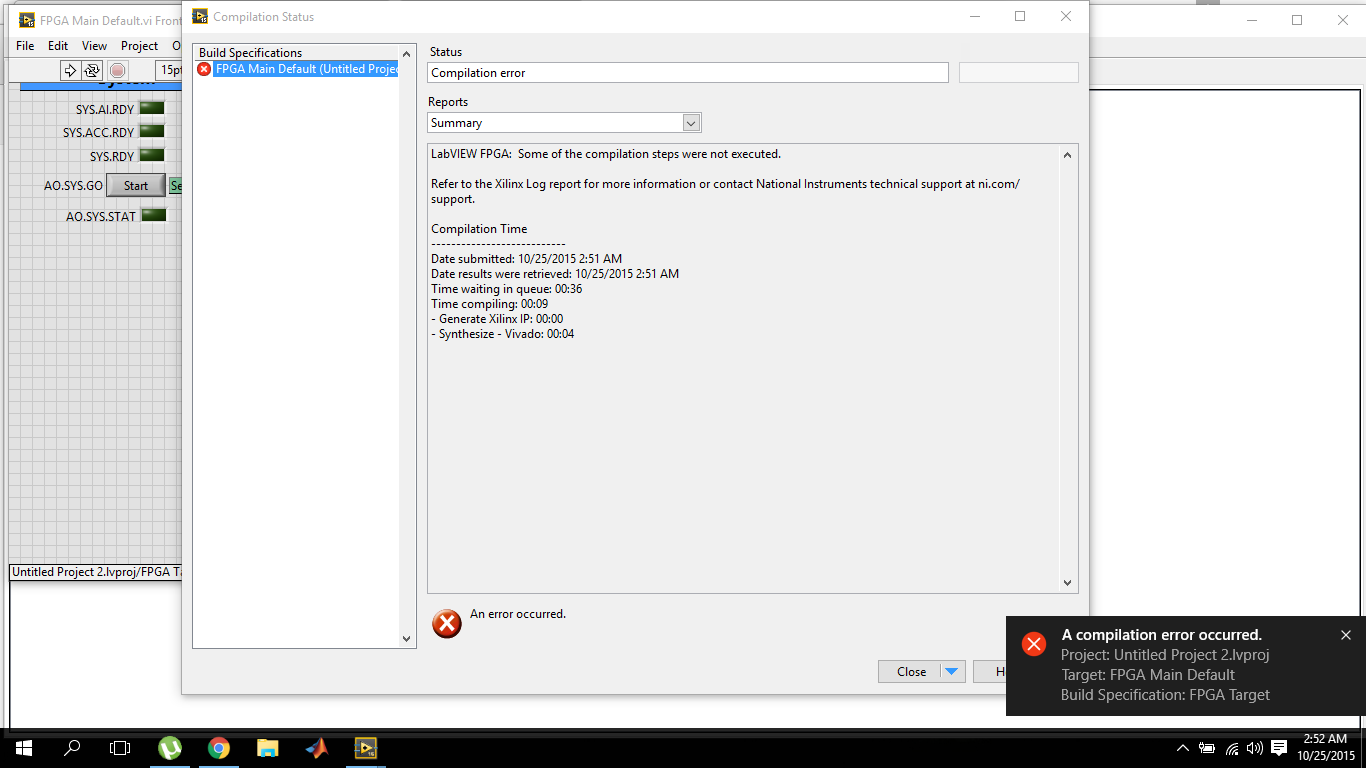

I've recently switched to LabVIEW 2015 and I'm working on OR myRIO. So also installed myRIO 2015 bundled software. The problem I have is that the compilation of fpga fails within 10 seconds.

and the target Xilinx journal report is empty

The first time when I tried to compile on 2015 version, it failed and the message box that failed came alongwith the avast antivirus warning for malicious activity. I reported it as wrong and now I tried several times with avast shield disabled control, but the results are the same. While the version of labVIEW 2014 works very well.

Now, I'm sure that there is something wrong with the installation of Vivado because this dll is part of it. The dll must be default in the2014_4\lib\win32.o directory C:\NIFPGA\programs\Vivado if you are using an operating system for 32-bit AND also in C:\NIFPGA\programs\Vivado2014_4\lib\win64.o If you use a 64-bit operating system. If the dll is not here, it is probably that the anti virus (I've never seen what happens to Xilinx but I have for other stuff).

I'm emphasizing the 2014_4 because LabVIEW 2015 uses Vivado 2014_4 while 2014 LabVIEW uses Vivado 2013_4. Since you have also installed LabVIEW 2014, you must have 2013_4 as well and if it works, you will find the dll I just wanted you make sure you check the correct directory for the Vivado 2014_4.

Download and install (reinstall or repair if already installed) 2015 LabVIEW FPGA Module Xilinx tools Vivado 2014.4. You can also use the DVD Setup if you have. It would be a good idea to do the installation with the disabled and even anti-virus try the first compilation the same. Try and let me know if the problem persists.

Kind regards

Tags: NI Products

Similar Questions

-

LabVIEW FPGA: Problem compiling look-up Table

Current versions of software:

LabVIEW 2014 SP1

LabVIEW FPGA 2014

Xilinx Vivado

I'm having a huge problem in trying to compile my LabVIEW FPGA code.

Some recall of the code:

It's all in a SCTL.

I am streaming in a FIFO DMA and comparing it with the values previously stored in the shift registers (which are initialized to 0 at the start of the loop) in the SCTL.

The results of the comparison are then piled into a U16 and loaded into a lookup table (I use the LUT - 1 d), and I'm so help this LUT to decide what value will be charged to travel to record for the next iteration of the loop, which, in any case, would be either the current values of the flow, or the post previous registry value.

(It's a triage loop)

I am able to run very well in simulation mode code, but when I try to compile, I get this error:

"The selected object has a built-in shift register that makes the output on a particular loop iteration correspond to the entries in the previous iteration."

Connect the outputs of the object directly to a minimum number of nodes of Feedback or uninitialized shift registers. You cannot connect the outputs to another object.

See using LabVIEW for more information on the objects with registers embedded offset. »

Someone at - it ideas why this happens, and what might be the possible solutions?

I'm tempted to break it down into separate loops, but I prefer not to because it is now a loop (and working in my simulation).

I found my problem.

Any time that a LUT is in a chain shift register, it cannot:

1. be part of a string of shift register that has a variable initialized

2. follow-up to no decisive structure, like a box structure.

I just moved the position of LUT and it works.

-

for the FPGA fifo compilation error

Hello

I downloaded the example RS232 FPGA program and tried to make a small change to it. The original is like that; See attached file "beforeModification.PNG".

I wanted to reread the amount of data still in the FIFO where I had read everything so I changed it to that. See attached file "withModification.PNG".

The target is using the compiler 13.4 Xilinx 7841R. I'm not in the section summary with the following error message;

Details:

ERROR: HDLCompiler:1566 - "C:\NIFPGA\jobs\K7I4YEj_RQC5mWo\NiFpgaAG_FPGA_Main.vhd" line 869: Expression has 11 elements; official ocountfullcount wait 10I'm currently running;

LabView 2012 SP1 f3

12.1, the R Series multifunction RIO of NOR

I'm doing something wrong?

Thank you

Andy

The problem disappeared when I copied the source files in a different folder

-

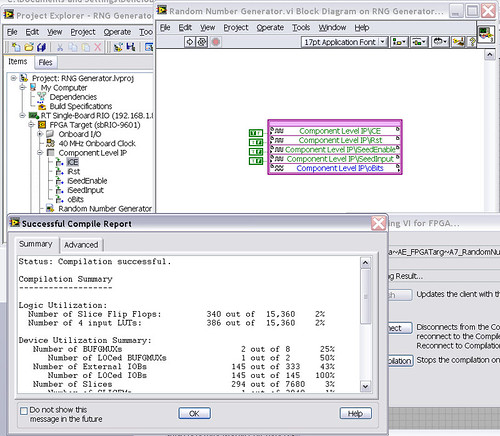

LabVIEW FPGA CLIP node compilation error

Hello NO,.

I work on an application for my Single-Board RIO (sbRIO-9601) and faced with a compile error when I try to compile my FPGA personality via the ELEMENT node. I have two .vhd files that I declare in my .xml file and all at this point works great. I add the IP-level component to my project and then drag it to the VI I created under my FPGA.

Within the FPGA personality, I essentially have to add some constants on the indicators and entries CLIP to my CLIP out and attempt to save/compile. With this simple configuration, I met a compilation error (ERROR: MapLib:820 - symbol LUT4... see report filling for details on which signals were cut). If I go back to my VI and delete indicators on the output (making the output pin of the CLIP connected to nothing), compiles fine.

I've included screenshots, VHDL and LV project files. What could be causing an indicator of the output of my VI to force compilation errors?

Otherwise that it is attached to the output ELEMENT, a successful compilation...

After that the output indicator comes with CLIP, compilation to fail...

NEITHER sbRIO-9601

LabVIEW 8.6.0

LabVIEW FPGA

Windows XP (32-bit, English)

No conflicting background process (not Google desktop, etc.).Usually a "trimming" error gives to think that there are a few missing IP. Often, a CLIP source file is missing or the path specified in the XML file is incorrect.

In your case I believe that there is an error in the XML declaration:

1.0

RandomNumberGenerator

urng_n11213_w36dp_t4_p89.vhd

fifo2.vhd

This indicates LV FPGA to expect a higher level entity called "RandomNumberGenerator" defined in one of two VHDL files. However, I couldn't see this entity in one of two files. If urng_n11213_w36dp_t4_p89 is the top-level entity, edit the XML to instead set the HDLName tag as follows:

urng_n11213_w36dp_t4_p89 Also - in your XML, you set the 'oBits' music VIDEO for output as a U32, however the VHDL port is defined as a vector of bits 89:

oBits: out std_logic_vector (89-1 downto 0)

These definitions must match and the maximum size of the vector CLIP IO is 32, so you have to break your oBits in three exits U32 output. I have added the ports and changed your logic of assignment as follows:

oBits1(31 downto 0)<= srcs(31="" downto="">

oBits2(31 downto 0)<= srcs(63="" downto="">

oBits3(31 downto 0)<= "0000000"="" &="" srcs(88="" downto="">Both of these changes resulted in a successful compilation.

Note: The only compiler errors when you add the flag because otherwise your CUTTING code is optimized design. If the IP is instantiated in a design, but nothing is connected to its output, it consumes all logic? Most of the time the FPGA compiler is smart enough to get it out.

-

Please help me for this problem "error starting compile step: make sure that a compatible version of Xilinx tools is installed in the location specified in the setup of LabVIEW FPGA.»

Look for the error on the Web site of or or on the forums. Take a look at the following links:

http://forums.NI.com/NI/board/message?board.ID=170&message.ID=381394&requireLogin=false

http://forums.NI.com/NI/board/message?board.ID=170&message.ID=205754&requireLogin=false

-

Internal software error of LabVIEW FPGA Module - 61499

I get the error next (in a pop-up window) in the phase of sompilation for the FPGA target with a vhdl IP. This error continues to occur even after restart LabVIEW and the PC. Someone at - it solved is this kind of problem before without having to re - install the software?

Here is the error information:

Error-61499 occurred at niFpgaXml_GetValue_String.vi<><><><>

Possible reasons:

LabVIEW FPGA: An internal software error in the LabVIEW FPGA Module has occurred. Please contact National Instruments technical support on ni.com/support.

Additional information: lack the tag required XML (/ CompileServerList)

As a first step, I can compile the vhdl IP node successfully. However, once when I'm running a VI with the FPGA, the bureau stop working. After that I restarted by force, it cannot perform the build of a vhdl IP node. Even without connecing to the jury of LabView, he pointed out errors before the end of the sompilation.

Interestingly, the screw which also includes nodes IP vhdl that I properly compiled before, I can still run the VI to the Commission and it works correctly.

Thank you

Looks like your ActiveJobsList somehow has been corrupted. I saw occur when computers are hard stop or blue screen during compilation. I don't have that LabVIEW 2014 installed on my machine, so your path will be a little different, and the file extension will be a .txt or .xml instead of .json, but try this:

Move the file "C:\Program Files (x 86) \National Instruments\LabVIEW 2014\vi.lib\rvi\CDR\niFpgaActiveJobList.json" (or your equivalent) out of the above directory (back it upward and delete essentially) and restart LabVIEW. Must regenerate the file and resolve the problem.

-

Compilation of LabVIEW FPGA on crash RT cRIO 9082

Hello

I developed a project of NI VeriStand FPGA (see Project.png) for a target of 9082RT cRIO (which contains 2 cRIO: 9205 & 9264).

I have develop a piece of software code to run it on the chassis of RT cRIO 9082 because I never used this kind of front frame.

The problem appears when I tried to compile the FPGA.

Start the compilation, I see a pop-up (see Msg.bmp) and failed to compile (cf.). Details.bmp).

With the following error, I'm sure that the failure is not because of my code.

Can you help me?

I found the problem that comes from the installation of 2012 more develop.

When the FPGA module and 13.4 Xilinx tools is installed, the DLL 'LIBBz2.dll' (of the NIFPGA\...\Common\nt\Xilinx record 13.4 "is not copied in the following"C:\Windows\system32"folder.

After I manually copied this dll to the "system32" folder, I restart labview and the compilation was successful.

A. Kaszubiak

-

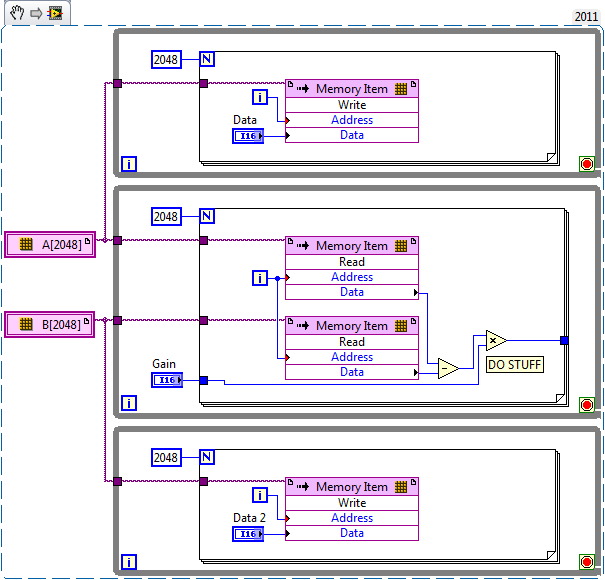

tables of fixed size in FPGA compilation error - how to implement a waveform control in an FPGA?

Hello

After being stuck for two days, please let me briefly describe my project and the problem:

I want to use the cRIO FPGA for iterative control of waveforms. I want to capture a full period of the waveform, subtracting a reference waveform period and apply control algorithms on this. Subsequently the new period of correction must be sent again for the output module OR. If it does not work, the captured waveform will look like the one reference after several iterations.

I am planing to create an array of size fixed for the capture and the reference waveform (each around 2,000 items for a given period). I use so 2 paintings of each elements of 2000. I use the function 'replace the subset of table' to update each element captured in the loop sampling and a feedback for each table node to keep in memory (I also tried shift registers, but then the berries do not have a fixed size any more and I can't start the compilation process).

If I try to compile the FPGA vi, I get the following error:

Details:

ERROR ortability:3 - Xilinx this application runs out of memory or met a memory conflict. Use of current memory is 4167696 KB. You can try to increase physical or virtual memory of your system. If you are using a Win32 system, you can increase your application from 2 GB to 3 GB memory using the 3 G switch in your boot.ini file. For more information, please visit Xilinx answer Record #14932. For technical support on this issue, you can open a WebCase with this project attached to http://www.xilinx.com/support.

ortability:3 - Xilinx this application runs out of memory or met a memory conflict. Use of current memory is 4167696 KB. You can try to increase physical or virtual memory of your system. If you are using a Win32 system, you can increase your application from 2 GB to 3 GB memory using the 3 G switch in your boot.ini file. For more information, please visit Xilinx answer Record #14932. For technical support on this issue, you can open a WebCase with this project attached to http://www.xilinx.com/support.

"Synthesize - XST" process failedBefore I added berries to my code I could compile the FPGA without problems. So, it seems that the tables are too big for the FPGA. :-(

Therefore, I would like to ask if there is perhaps a better method to implement my problem in LabVIEW FPGA? How could avoid the tables to save my waveforms on a period?

Thanks a lot for your help in advance.

Best regards

Andreas

Unfortunately, the LabVIEW FPGA compiler cannot deduct stores shipped from berries (yet). When you create these two large paintings, you are creating essentially several registers very, very large. Just by looking at your picture, I guess that there are at least 4 copies of each of the tables.

You want to use LabVIEW FPGA memories instead. You can create memories outside the loop and then read/write them where you are currently referencing the berries. The only change that you really need to do is to break down your treatment in scalar operations. I have attached a simplified version of your plan, I hope it helps. Let us know if you have any other questions.

-

LabVIEW FPGA: An internal software error in the LabVIEW FPGA Module has Unknown

Sir/Madam,

Note Labview 2012 SP1 installed about 2 weeks ago.,.

Accident occurred during the compilation of an fpga vi who worked satisfactorally in the past.

When I restarted and went to the message recomplile "LabVIEW FPGA: an internal software error in the LabVIEW FPGA Module" see attached picture of popup.

I reinstalled Labview in its entirety and backed out the changes I made to the vi but still get the same message.

Thanks in advance

Daryl

It turns out that the question was in the VI and not of LabView FPGA module as the message may indicate. I created a vacuum vi, cut and pasted items in this from the vi error and recompiled and it ran very well.

Somehow the vi has been corrupted internally.

Thank you it's fixed.

-

I'm converting a piece of code from 8.5 to 2011. When I tried to compile the fpga vi to a bit file, I get the error attached. Why is this? Thank you!

The thing is that the only solution that I found about this error is to install a patch or repair/reinstall Xilinx or LabVIEW FPGA tools.

Christian

-

FPGA compilation error sbRIO 9632

Hi guys,.

I'm trying to write a simple piece of code to send a PWM signal to a PIN on my sbRIO-9632 (starter kit 2.0) to order a servo. I used the example of 'control a servo using PWM' and my code is pretty much the same. When I try to generate/compile the FPGA VI, it stops after only 4 to 6 minutes, saying an error has occurred. The compilation appears to hang during the process of the "card".

The example is for a sbRIO-9631 so I created a new project for my robot Robotics and changed the PIN e/s that I use (Port5/DIO9). I search through forums but cannot find a solution to this :/

I have attached my code and the XilinxLog file with it.

Thanks for any help!

MortZ

Hello

Sorry for the late reply! Have you made progress?

Unfortunately, your zip file seems to be disabled on my PC. How it has been compressed?

So what I meant by remove the digital Pulse.vi to generate, is to see if it affected the compilation. Please see if you can compile the FPGA code with the following approach:

Create the new project > add your target sbRIO > add the VI attached to this post to your FPGA target > compile

I think it would be beneficial to you to see if the problem is the compilation itself or the code you are trying to compile.

In addition, you have any another available PC? Might be a good idea to see if your code compiles on another PC.

Please make sure you have LabVIEW Real-time and LabVIEW FPGA installed (it should come with the Robotics module, but I recommend that you check that they have indeed been included).

If the build process fails to map no matter what you do, I propose the following: make sure that the target passes a self-test of MAX. reinstall the Xilinx tools (only if it seems that the issue is not with the code, but with the compilation process itself).

Good luck

Best regards

Christopher

-

LabVIEW FPGA failure with compiler Xlinx?

I'm in LabVIEW FPGA 8.6 with NOR-RIO 3.0.1 (to 8.6). When I compile a simple program, I get the notorious:

«Error starting compile step: make sure that a compatible version of Xilinx tools is installed in the location specified in the setup of LabVIEW FPGA.»

I checked the FPGA compile server and I ran the utility fixTlink.VI with no improvement. This produces two identical PC, neither one having a FPGA installed card.

Any ideas?

After further analysis, the problem was to be in our facility in LabVIEW FPGA 8.6. Using the correct Installer of NEITHER solved the problem.

This thread is now resolved.

-

The project-centric issue of peer to Peer with an external compiler in LabVIEW FPGA

Hi all

FPGA OR Version: 14.0

I have an application developed in LabVIEW interfacing FPGAs developed in LabVIEW FPGA making of peer to peer Communications.

Everything works fine.

I try on the port to Visual Studio 2013 (on the same PC) and am able to communicate with the FPGA very well using the C API.

However, I have a problem now with the help files or the peer supported external compiler peer.

I get these errors:

1. cannot open the file source 'PublicIncludes/nistreamCommon/prefix.h '.

2. impossible opening the file source 'PublicIncludes/nistreamCommon/postfix.h '.

in

c:\Program Files (x 86) \National Instruments\Shared\ExternalCompilerSupport\C\include\nip2p.h

in my project...

I looked in the folder c:\Program Files (x 86) \National Instruments\Shared\ExternalCompilerSupport\C\include\ and the PublicIncludes\nistreamCommon folder does not exist.

What I am doing wrong?

Hello!

It seems that you have worked with another engineer of Applications on this issue. For the love of documents, the nip2p library is not supported in CVI. There has been cases where users were able to get this work to comment on the two header files.

Thank you!

-

Compilation of FPGA - real formal error on the cost of the port cannot be an expression

Details:

ERROR: HDLCompiler:192 - "C:\NIFPGA\jobs\BPO5kq2_O6tyN2U\OC4_Sine_Cosine_LUT_Constant_Amplitude_dash_optimised_vi_c.vhd" line 1408: real formal on the cost of the port cannot be an expression

ERROR: HDLCompiler:854 - "C:\NIFPGA\jobs\BPO5kq2_O6tyN2U\OC4_Sine_Cosine_LUT_Constant_Amplitude_dash_optimised_vi_c.vhd" line 69:Unit ignored due to previous errors.

File VHDL C:\NIFPGA\jobs\BPO5kq2_O6tyN2U\OC4_Sine_Cosine_LUT_Constant_Amplitude_dash_optimised_vi_c.vhd ignored errors

-->The compilation happens to step "using the unit felt" but then stops soon after with a compilation error.

The line in question (1408) refers to the output of a "Reinterpretation FXP" node with the text

Cost => (others-online '0'),

in the part of port of the code card. This is the output of the FXP reinterpret node is directly connected to an indicator in a VI sub whose output is then entered directly at a crossing high multiply node. The code is part of a cosine sine LUT I programmed. She used to compile without a problem, but I think I know where is the problem. In one case, I have used only the sine of output of the algorithm and theory, Xilinx can optimize away from the part of cosine. I have two instances of this VI in my code and looking at those generating any errors, the output is associated with a cosine indicator.

Cost-online s_Cosine_2434,

It seems that the track is essentially optimized away, but the compiler, Xilinx has a problem with the flag being present on the sub - VI but the idnicator is not used anywhere. As a result, the cost gets set to an invalid value. I guess close to reinterpret it FXP at the exit of the Subvi is an important aspect of this problem.

I think I know enough now to fix this (remove the path manually by duplicating the sub - vi), but it may be useful for future bug fixes feedback in the FPGA module. It is not the first time that this kind of removal of incorrect code me has given problems, but this is the first time I could clearly identify the problem.

Shane

Hey Shane,

Looks like someone filed a bug report on it a month or two ago. It's the CAR # 475397 if you want to check for it in the list bug fixed for 2014 SP1.

-

Error when create control LabVIEW FPGA CompactRIO

I have error when you try to create a new model of LabVIEW FPGA CompactRIO control project. I tried with LabVIEW 2014 and 2014 SP1 update. This error always occurs.

Please help me with this.

Kind regards

Thang Nguyen

Hello

I fix the problem by removing LabVIEW 2014 SP1 and reinstall again. After the reinstallation of LabVIEW, I create the project template.

Kind regards

Maybe you are looking for

-

Photos automatically remove and duplicate

Why my duplicate photos and why some endangered. I'm very adamant on using iCloud as my main library, but not my only. Thanks be to God. I noticed that my pictures will disappear at the time and some years ago will duplicate as if they were taken rec

-

Subscribe to the news FEED in Thunderbird

When I go to an RSS feed on a website I get given the pop - up "Subscribe to this feed using..." option "and Thunderbird in the drop-down menu options. When I click on Subscribe that everything that happens is it switched to Thunderbird but no flow a

-

Is it possible to add acronyms in the dictionary of AutoCorrect on my MacBook Pro mid 2012? Often as I'm looking for something or typing an e-mail, AutoCorrect will change my acronym and it makes me or send an e-mail that makes no sense, or I spend 5

-

E5 - 572 G-5577 cannot function properly 840M 2 GB dedicated VRAM nvidia

Hi, I recently bought Acer aspire model E15 E5 - 572 G-5577, which came with i5 - 4210 m (2.6 to 3.2 Ghz), 8 GB of RAM, Nvidia GeForce 840 M 2 GB dedicated VRAM, 1 TB HDD and freeDOS. Since Win8.1 x 64, I received for my birthday, I bought this lapto

-

Photosmart 6520: photo-editing documents/prescan

I seems to have "lost" the ability to 'Edit' a docment/photo before parsing and now can only scan the image, graduating to my computer. Have recently spent ro windows 10