LV FPGA Instruction framework

Hello

NEITHER uses the framework of education for almost all their FPGA designs today. I would like to get a deeper understanding of it and start using it in my own creations. However, I have not found all the resources that describes what classes should I create on my own, which classes they must inherit, what methods need to be overridden etc.

Are there guides development of framework of Instruction or tutorials somewhere?

Best regards

Anders

Tags: NI Software

Similar Questions

-

MyRIO FPGA read framework signals SENT

Hello community,

I now have a myRIO with Labview 2013. I try to read a digital signal to a sensor on the port DIO0 (C-Port). It works very well. The problem is that I don't know how to find the start (the SYNC nibble) of the frame SENT - and how it works with the ticks of the clock / time clock of the FPGA (40 Mhz) system. I do not understand the meaning of the clock. ticks of the clock.

The next problem is to measure the time between a front down to falling edge. In fact I can detect every falling edge of the signal SENT but I cannot measure the actual time between them. How can I measure the real time based on the system FPGA clock time? The nibble of SYNCHRONIZATION were all 56 time graduations. But how long are 56 ticks?

Best regards

Basti

Hello, Alexander.

Thank you. It works very well.

Now my problems are solved. The main problem was to build something that is capable of converting 56 ticks of the SYNC signal SENT for correct ticks of the sampled signal. The two frequencies, the Signal SENT (333kHz) and the sampled signal (40 Mhz) are different, so I divided the frequency of the signal sampled frequency of the Signal SENT - (factor of about 120). Now I can convert 56 ticks to correct the number of ticks of the sampled signal and I can find the SYNC - Puls in FEEL. The result of 56 times the factor of 120 ticks is 6720 ticks. So, I convert ticks to the correct frequency.

Thank you very much for your help!

Best regards

Sebastian

-

Instructions for the removal and reinstallation of .NET Framework on windows xp 32-bit

I need full instructions with links of web page to remove all versions of net and then put it back. I have a copy of an e-mail that has it all, but I don't know how to get my copy in a document where I can use the web links.

You must may (or may not) .NET Framework 1.1.

Of http://blogs.msdn.com/b/astebner/archive/2009/04/20/9557946.aspx

Most of the applications that have been created for the .NET Framework 1.0 or 1.1 will automatically use the .NET Framework 2.0 instead if it is installed on the system. In most cases, this means that you do not need to keep the .NET Framework 1.0 or 1.1 is installed on your system if you have already installed .NET Framework 2.0.

However, there are some applications that are configured to require a specific version of the .NET Framework, even if later versions of the .NET Framework installed. If you have any application like this on your system and try to run without having to install the .NET Framework 1.0 or 1.1, you will get an error message that resembles the following:

---------------------------

MyApplication.exe - .NET Framework initialization error

---------------------------

To run this application, you first must install one of the following versions of the .NET Framework:

v1.1.4322

Contact your application Publisher for instructions about obtaining the appropriate version of the .NET Framework.

---------------------------

Ok

---------------------------In the above error message, the version number will be v1.0.3705 if you install the .NET Framework 1.0, and it will be v1.1.4322 if you need to install .NET Framework 1.1.

If you end up seeing error messages like this one, you can re - install the .NET Framework 1.0 or 1.1 in order to fix the errors. If you end up seeing errors like this, then you don't need to worry about re - install the .NET Framework 1.0 or 1.1.

-

Instructions to improve the framework of a mask

Hello.

Consider that I ended up making a mask.

I would like to improve that part of this mask because I see that whole mask is good, but not a part.

How could I do to improve the choice between two points?

I want to smooth out the choice between two points.

Thank you.

To get the right image. No not Alt-click on the mask that shows just the mask in Photoshop image area. The target just the layer mask leave the active composite view that you set the filter, you'll be able to get a preview of the effect of the mask will have on the composite. Look at a mask just is like a blind man making such an adjustment, perhaps using a little view that they always have to do the mask.

-

Carved frame. Camera Basler with FPGA

Hello!

I use a 340kc of acA2000 of Basler camera controlled by an FPGA PCIe-1473R.

After a few adventures, I finally changed and changed the configuration of TAP with this post.

http://digital.NI.com/public.nsf/allkb/EA1727D8D620B81F8625797B0072257C

With just the change in the FPGA, the camera works and takes pictures successful, however the framework is divided into four images (all identical but light intensity).

When I also change the host code, only an image appears in the frame, but certainly not a good image, as previously.

Someone knows why maybe this problem happening?

Thanks for your help.

I think I knew what is happening. I believe that section of the knowledge base that you read is incorrect. We will solve the problem together and I'll correct the article if necessary.

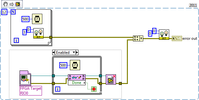

Let's talk for a little bit of what's going on. The two keys are 10 bits each, but they are stored in the 16-bit data type. The two pixels must collect the FPGA to the host with a DMA FIFO. For more convenience, the code uses a single DMA FIFO even if there are two taps. The article suggests that you must combine numbers 16 bits 2-in-1 32-bit number and then send it in the DMA FIFO. There are a few problems with this: first, the DMA FIFO has been configured for 16-bit, so half the data is being deleted. In addition, the code on the host computer is dividing the 16-bit data in 8-bit, which is not correct.

I think it would be better to change the DMA FIFO to support 32-bit data. You can do this by opening the LabVIEW project and right click on the host 16 DMA, select Properties, and then change the type of data in U32. After that, you must program the code on the host computer to divide the number. You will get then two tables (one for each). I think it will reconstruct the image correctly if Interleave you just these two tables.

I have attached a few images. Try it and tell me if this works. If so, I will update the documentation.

Jeremy P.

-

USRP RuntimeError: Please update the firmware and FPGA images for your device.

Hello

I have an Ettus USRP N210 with a surfboard RF WBX running FPGA firmware version 4.

2009 LabVIEW and NOR-USRP 1.1

When I try to run one of the USRP VI OR as devices to find it displays the following error code:-1074118627

"niUSRP Devices.vi find

a length or configuration error has occurred."

Code: 1440

Details: RuntimeError:

Please update the firmware and FPGA images for your device.

See application for USRP2/N-Series notes for instructions.

Compatibility of the Protocol expected number [7-11], but received 12:

The version of the firmware is not compatible with the host code generation. »I can communicate with unity on Linux using UHD machine and the utility Configuration NI USRP can see the device, but firmware update is not possible, probably because of my IP ending in 221. Latest firmware Ettus was recharged via Linux UHD.

Looks like my firmware again? I am not allowed to download the old versions of the FPGA firmware.

Can someone help me with this problem please?

With respect,

-Sigurd has.

Hello Sigurd,

The NOR-USRP driver requires a specific firmware and FPGA image to be downloaded to the USRP to exploit.

You can use the utility of Configuration USRP download appropriate firmware and FPGA image to the usrp.

This knowledge base article will help you: how update the Firmware and FPGAS Images for N2xx and NI 292 x USRP

-

Typedef reference FPGA not updated in the private class data

I have a FPGA reference related to a typedef that is passed in a LVOOP object. If I change the FPGA of computer simulation of dev to the use of the actual hardware, all references to the typedef are updated which are controls on a diagram. But the typedef in my private class data seems not not to date, so I'm broken son until I replace the control to private data of my class with a copied from my block diagram. Has anyone seen this? Is there a CAR already? I can create a small project to reproduce if necessary.

Edit: this also seems to happen when I change bitfiles or change to open a VI a bitfile opening in the Configure dialog box open FPGA VI.

Hi Greg,.

I was able to reproduce your problem thanks to your easy to follow instructions.

I noticed that type def successfully by checking "Bind FPGA host of reference to the type definition" in the open FPGA VI reference configuration. What does not automatically update is the Issue.ctl of OBJECT-oriented programming, which has a nested type definition in the private data reference.

The fastest solution, that I could find was to right click on "Issue.ctl" in the project, and then click Save. This problem immediately solved the broken wire error.

While configuring open FPGA VI reference has the practical ability to bind to the def of type, it does not broadcast this change to data private to the class. I call not this bug, but I can see how you want it works this way.

I would recommend you post that on theExchange of ideas (I see you're already regularly here).

-

Open FPGA references change to no. target when compiled with executable in time real start

Hello again you useful forum fans! I have a problem that I hope someone can give me a hand with.

I have a project that has a Windows component and a component of the target in real time, that are running on a hypervisor type NI PXI-8110 system. Communication both sides between them using shared variables.

On the real-time side, I have four FPGA targets who are reading and writing various analog and discrete inputs and outputs. I several periods loops which opens a reference to one of the FPGA targets during the first call, then pass this reference in several subVIs that read and write to panels prior to the FPGA. The loops the FPGA reference thus made available and reuse it in the next iteration through the shift registers. Each FPGA target has only a single reference open to him. One of the loops is using the FPGA reference directly and does not pass it in any subVIs.

It all works very well in the development environment, I can read and control inputs and outputs FPGAS via the front panel of the application of the side Windows. It also works very well if I start the game real time in the development environment, and run the code of windows as a stand-alone executable file.

However, when I compile the code in real-time in an executable startup and deploy it to the target, it does not work. I enabled debugging on the executable, and when I connect to it via the operation-> debug executable in the menu, I see an arrow broken at execution. Further investigation shows that each of the four open screw reference FPGA is now empty, the text under them is "no target" and the thread for reference on their part to my first Subvi is broken. I need your help to understand how to operate as it does in the development environment.

I followed the instructions of these two knowledge base articles to compile and download the bitfiles FPGA on the FPGA target and execute on start or restart:

http://digital.NI.com/public.nsf/allkb/39795847AC67296D862575FB0046944F

http://digital.NI.com/public.nsf/allkb/BC513C2A0DC29C89862574BF0002B0B9?OpenDocument

Open FPGA reference screw are configured for the FPGA to build specifications that I created for each target in the LabVIEW FPGA project.

I called technical support, NO phone, and yet were able to determine this one out, so additional "brownie" points if you do!

I would offer you the same no detailed screenshot that I have (I can't give more detailed code out because its owner, unfortunately), but apparently the forum doesn't like my image file, as I can't seem to load.

I would offer you the same no detailed screenshot that I have (I can't give more detailed code out because its owner, unfortunately), but apparently the forum doesn't like my image file, as I can't seem to load.Please let me know if you have any ideas regarding what is happening! I appreciate it.

Jon,

I'm always up for the challenge. Have you tryied recompile the FPGA VI that accesses the RT VI? I also suggest to try and open the bitfile instead of the FPGA VI. You run in dynamic mode (this is not a suggestion, it's just a question)? There is no difference if you try to open the FPGA VI reference outside the while loop, then past the reference to use inside the while loop without shift registers, then close the reference to the FPGA VI outside the while loop?

Let me know if these suggestions makes no difference.

-

Hello

I try to use the Module States transitions with the FPGA Module, and after analysis of the problem, it seems that I won't run the transitions on the FPGA in asynchronous mode. In other words, the FPGA has several operational States (an acquisition loop, 2 simultaneous control loop regions - each with subreports), and I vi FPGA of the transition between States from the triggers of the façade of my host vi.

So I thought I could run the transitions in asynchronous mode is used on the FPGA and send external triggers and data from the host of vi in response to my entry façade. The thing is, I can't run asynchronously on the FPGA transitions.

Each of the subreports on FPGA should work indefinitely, until to be instructed to change the host vi - for example. Control States, the measure States, idle States

What is the other recommended way to fix this?

Thank you

A common strategy is to send a trigger NULL (default) when he has to make any changes. This trigger acts as a kind of heart rate, causing the transitions continue to work. Then, you can send a specific trigger when you want the transitions to change States, etc.

-

You try to run the scan mode and mode interface fpga at the same time is causing errors

I'm reading a 9236 9237 and a 9215 with the scanning engine and read from two 9211 modules with the fpga. It's because I need to acquire to 200 Hz with the 9236 9237 9215 but maximum rate of the scan engine is limited by the slower module in the system, which in this case is the max of 15 hz the 9211.

So to use both interfaces (scan engine and fpga), I followed the percisely given in this article for instructions.

1. the project has created and added the peripheral crio using the interface of the scan engine.

2. Add the target fpga and drag and drop the 9211 inside modules

3. has created the fpga in interface file with and compiled with no error.

4. interfaced with the file fpga at almost exactly the way the sample project of "getting started with 9211' by using the engine of analysis in the interface with the other modules.

5. after the errors to discover that I created a VI that tests for just the portion 9211 code (called "thermocouple FPGA method Test.vi")

The data returned by the interface fpga was nothing else than zeros on all channels, even if thermocouples were hooked on some of them. (all zeros as entries in the convert temperature vi gives-410, 6160 degrees F, if you happen to have the material to try this.)

I get the following error from the open fpga vi reference:

code error-61141

"Thermocouple method Test.vi FPGA.

Activities FPGA:Open FPGA interface reference.

Reserved outside LabVIEW FPGA: turns The RIO Scan Interface. You must set the mode Interface FPGA chassis in order to unlock the FPGA. »It's extremely frustrating, because as I explained, I've been very attentive not only follow the instructions for concurrent fpga and analysis but also to model my VI by the example of VI, even if only for the moment, just to try to work things out.

Any help would be appreciated as I need to fix this for the further development and I am somehow in a lack of time. I opened a support ticket (reference #7256226), but the app engineer had no time to answer.

My system:

cRIO-9014 controller RT with crio-9104 bottom of basket.

LabVIEW 2009

Latest drivers and peripheral software pc and rio (RIO scan 3.2 engine support june2009)

rex1030 wrote:

I'm reading a 9236 9237 and a 9215 with the scanning engine and read from two 9211 modules with the fpga. It's because I need to acquire to 200 Hz with the 9236 9237 9215 but maximum rate of the scan engine is limited by the slower module in the system, which in this case is the max of 15 hz the 9211.

This should not be the case. 9211 data will not update with each sweep, but you should be able to run the scan faster than 15 Hz without problem. Do you have specific issues with this?

So to use both interfaces (scan engine and fpga), I followed the percisely given in this article for instructions.

1. the project has created and added the peripheral crio using the interface of the scan engine.

2. Add the target fpga and drag and drop the 9211 inside modules

3. has created the fpga in interface file with and compiled with no error.

4. interfaced with the file fpga at almost exactly the way the sample project of "getting started with 9211' by using the engine of analysis in the interface with the other modules.

5. after the errors to discover that I created a VI that tests for just the portion 9211 code (called "thermocouple FPGA method Test.vi")

You can try making sure that the chassis is set to mode Interface FPGA and the setting is deployed. I wrote that article that you referenced says will select the deploy option later and not explicitly speak to deploy the chassis later. Run a VI with a reference open FPGA vi not automatically deploy chassis settings if you need to do it explicitly. Try the following steps.

1. right click on the frame element and select Properties. Make sure that the Interface FPGA option button is selected. \

2. right click on the frame element and select deploy.

3. repeat your VI.

The data returned by the interface fpga was nothing else than zeros on all channels, even if thermocouples were hooked on some of them. (all zeros as entries in the convert temperature vi gives-410, 6160 degrees F, if you happen to have the material to try this.)

I get the following error from the open fpga vi reference:

code error-61141

"Thermocouple method Test.vi FPGA.

Activities FPGA:Open FPGA interface reference.

Reserved for LabVIEW FPGA outside: The RIO Scan Interface is running. You must set the mode Interface FPGA chassis in order to unlock the FPGA. »The likely cause of this error is that the setting of the FPGA Interface on the chassis has not been deployed. If the chassis is still Mode Scan fixed personality bitfile will be loaded on startup and the FPGA will be locked.

It's extremely frustrating, because as I explained, I've been very attentive not only follow the instructions for concurrent fpga and analysis but also to model my VI by the example of VI, even if only for the moment, just to try to work things out.

I'm sorry that you have had difficulties. Assuming that I'm wrong about the source of your problem, it seems we have to update less than Ko to include the deployment step.

Any help would be appreciated as I need to fix this for the further development and I am somehow in a lack of time. I opened a support ticket (reference #7256226), but the app engineer had no time to answer.

My system:

cRIO-9014 controller RT with crio-9104 bottom of basket.

LabVIEW 2009

Latest drivers and peripheral software pc and rio (RIO scan 3.2 engine support june2009)

-

Hello

I use a Subvi to pass some parameters from the host to the FPGA using the function "read/write control."

The Subvi takes a "FPGA reference In" as the input and provides a "FPGA reference Out" output.

The problem is that whenever I have a few changes to the FPGA code (for example, I change the type of an input/output), the wires entering the Subvi are marked as broken since the reference FPGA has changed.

Now, I know that I can solve the problem by opening the Subvi, right-click on the FPGA reference and configure it. But this must be done manually and I want my Subvi to automatically detect any change.

Is it possible to do?

Thank you

Dragis says:

You can create a typedef and to use this type for your subvis controls/indicators. You will need to manually configure the typedef, but at least, just do it in one place.

You need to manually configure the FED type. You need create the def type once and replace all your existing references with her. Then on the block diagram, find the function of reference FPGA VI open and right-click to set it up. At the bottom of this box, you will see an option "Bind to Type Definition". Check, then enter the path to the type definition, that you have created. Close the dialog box. The type definition will now automatically update to reflect changes to the FPGA VI. See:ttp://zone.ni.com/reference/en-XX/help/371599E-01/lvfpgahosthelp/fpga_using_subvis_in_host_vis/ for more information and if you use a LabVIEW 2009, follow the instructions in http://digital.ni.com/public.nsf/allkb/2906287B989006EA862576AB005BE08E

-

Hey Gang,

I spent the day to set up a new system of cRIO and a new installation of LV2012 RT and FPGA Softmotion.

Our system uses a CAN interface, which, we learn, requires the use of FPGA mode. Maybe this isn't a bad thing, because we are concerned about the speed of the scan mode. I developed an FPGA application before.

My main concern is right now, to get the job of control of movement stuff. Our movement is a NI - 9514. I hope there is a way to use the SoftMotion modules with the FPGA interface. Otherwise, the movement FPGA examples look REALLY discouraging!

All I do is homing and simple relative motions. I enjoy all help/advice on the simple/fast way to get there.

Thank you!

Roger

Hi Roger,

You can use the 9514 without using the "formidable" examples using the cRIO in hybrid mode. There are good instructions on how to do it here. A quick summary, is to put the modules you want to use in scan mode under the chassis and modules you want to use FPGAS in the FPGA. When you compile the FPGA bitfile, RIO scan interface is compiled for modules that are under the chassis so that you can use in scan mode. A few warnings:

- The FPGA VI must be running to use the 9514. When you are in scan mode, the FPGA runs automatically without requiring you to do so. However, in hybrid mode, the FPGA does when you run it explicitly.

- The FPGA VI should work for deploy you the settings of the axis of the target. This can be a bit awkward during development when you make changes to the configuration of the axis. Usually, you run the FPGA VI using the open FPGA VI reference in a RT VI. However, when you run a RT VI, it checks to see if the deployed data are compatible with the project data and if not, invite you to deploy. Don't forget, however, that you cannot deploy your FPGA VI because is not yet running (since it won't work until the open FPGA VI reference runs). When you try to deploy, you will get an error (I think it's something like "E/s Module not found"). What I do usually is during development, run the FPGA VI manually (by pressing the run button). You can then run your VI RT which uses the FPGA VI reference and everything will work. You will encounter this problem only if you change the configuration of the axis of the project (and so won't be a problem for your final application when changing your aern can't axis settings). If you change the configuration of the axis programmatically, you do not experience this problem.

As a note side for those who use the 951 x modules of movement, unless you really need to do something custom, you must use the modules of 951 x in scan mode. The performance is better in scan mode it is using FPGA (assuming you want to use the API SoftMotion high level (EXVIs, blocks of functions or properties/methods)). When you use FPGA mode, there is further delay to obtain the data of the FPGA in the SoftMotion engine. In addition, you are always coupled to the scan engine! If you get the worst performance, a more difficult experience, and you don't even remove the need for the analytical engine. There are valid reasons to use the modules of 951 x on the FPGA (for example custom control loops), but most applications I've seen use FPGA would be better served by using the module in scan mode.

Thank you

-

Drivers Xilinx/Multisim and Labview FPGA

Where can I find drivers for my FPGA OR if I use Multisim/Xilinx and NOT of Labview? All the links I found are Labview be installed. However, the explicit manual FPGA indicates that you can use Multisim/XIlinx ISE in place.

OK, I tested just outside. The Driver of LabVIEW 2013 DEFB contains 2 separate components, the driver and Module FPGA support. If you run this installer, it won't check if you have LabVIEW FPGA installed unless you check the box for LabVIEW FPGA support.

I can change the text in the Installation Instructions to read "LabVIEW FPGA 2013 is required to install the LabVIEW FPGA Module Support component installation".

-

LV FPGA workflow nested CLIP w / NI SMU-6591R

Hello

I develop an application on a NI-SMU-6591R Board. My installation also includes a SMU-1085 w chassis / controller 8135.

Goal: set up a VHDL project prior to the Commission of 6591R. Given that the application requires access to 2 ports Mini SAS HD and the VHDCI connector on the front of the 6591R (physical front) a CLIP nested is the only option here, isn't it?

I am quite new to the LV FPGA framework. In order to understand the flow of the whole project, I would like to launch a trivial VHDL design on the 6591R: a D-FlipFlop edge triggered w / Syncronous reset. I have attached the the D - FF and the wrapper of CLIP VHDL code.

I would like that (1) a little (LV::boolean/VHDL::std_logic) to pass the port D of the D - FF VI (name FDF/D) and (2) drive the LEDs of the Board of Directors according to the signals of outputs (FDF/Q and FDF/QB). Also, I want to read (3) the same outputs (FDF/Q and FDF/QB) back to the VI flying two Boolean flags.

Following the white paper OR, I have:

- Managed to create a XML interface of the import VIDEO Wizard, import the 2 files VHDL (D - FF and its packaging).

- Selected the ELEMENT created in the IP-level component properties window. The LV_DATA_IN (host2fpga) and LV_DATA_OUT (fpga2host) I/O appear in the project tree, under the CLIP icon.

- Created a new VI under the FPGA device with an infinite while loop. Inside the loop, I dropped the LV_DATA_IN and the LV_DATA_OUT e/s and connected with a control (to LV_DATA_IN) and two indicators (of LV_DATA_OUT).

First of all, why in a simulated execution mode, the behavior of the indicators is totally random? They are not connected to one of the connectors 6591R...

Linking the FPGA VI, he reacts to any change in the control LV_DATA_IN button... Why?

The design works as expected in Vivado both in behavioral simulations and post-synthese.

Before asking here, I tried to understand it on my own. I have read all the documentation that I found on campus (I got access to LV Core1, Core2, Core3 and FPGA course material) and on the internet.

What is still missing me?

TY for your kind help!

-

by deployed/launched RT App with "Open FPGA" no executable program

Howdy-

According to the instructions in these links:

http://digital.NI.com/public.nsf/allkb/A7DBA869C000B5AE862570B2007C4170?OpenDocument

http://zone.NI.com/DevZone/CDA/tut/p/ID/9640

and others I've read, I wrote a PC-side VI which FTPs a Source of RT dist. During my cRIO (9076), then use it "Run VI' method to launch the application.» For test purposes, the RT VI has a call option to a simple VI FPGAS:

With the FPGA disabled call, everything works fine. With the call of the FPGA, the method of "Run a VI" in the code PC side returns error 1003: "the VI is not Executable.

The cRIO VI works in interactive mode (front) with and without the call FPGA.

Any ideas why this happens?

I'm under LV 2011 on the PC and OR-RIO 4.0 on the cRIO. I've included with this post project files if it can help.

Thanks a lot and have a nice day.

Well, it seems that I had accumulated a bad bitfile associated with the FPGA VI (there were 2 of them in the bitfiles folder, where only should have one). The solution was to remove the old bitfiles and rebuild the FPGA of the project part.

Maybe you are looking for

-

How to roll back the update of Firefox 29? I hate it.

I got the update of Firefox 29. I don't like it and removed features (for example, the bar add-on). How to restore? I have to completely uninstall Firefox?

-

Please help me with my Apple Airport Extreme

Aabout 2 weeks ago, we had a storm really come through the East Texas up to this point my router was working fine. The first week, I called and my ISP said that we had a power outage in the area and I thought that I thought this would happen so I wai

-

How to clear the buffer in TCP/IP

HIII can someone explain to me how the cleat of the TCP/IP communication buffer

-

I added two items to the Tools menu in LabVIEW by placing the screw in «...» File \LabVIEW 2014\project. Now, how can I disable/fadeout one element? Is it possible to do it by programming?

-

I have a Photosmart C8180 All-in-One printer and my OS is Windows 7 64 bit. I get the ink system, cannot print failure error message. I tried to unplug the power cord from the printer and wait 60 seconds before it reconnected. I can still print it. I