Transitions running on FPGA

Hello

I try to use the Module States transitions with the FPGA Module, and after analysis of the problem, it seems that I won't run the transitions on the FPGA in asynchronous mode. In other words, the FPGA has several operational States (an acquisition loop, 2 simultaneous control loop regions - each with subreports), and I vi FPGA of the transition between States from the triggers of the façade of my host vi.

So I thought I could run the transitions in asynchronous mode is used on the FPGA and send external triggers and data from the host of vi in response to my entry façade. The thing is, I can't run asynchronously on the FPGA transitions.

Each of the subreports on FPGA should work indefinitely, until to be instructed to change the host vi - for example. Control States, the measure States, idle States

What is the other recommended way to fix this?

Thank you

A common strategy is to send a trigger NULL (default) when he has to make any changes. This trigger acts as a kind of heart rate, causing the transitions continue to work. Then, you can send a specific trigger when you want the transitions to change States, etc.

Tags: NI Software

Similar Questions

-

Code error-61499 when you run an FPGA VI on favorable computer with e/s Siulated

Dear Forum

I have a problem running my FPGA VI on simulated with e/s Comupter development

I created a test bench, as described in

http://zone.NI.com/reference/en-XX/help/371599D-01/lvfpgaconcepts/test_bench_tutorial/

It works very well. I can read a write i/o nodes

But when I insert a control node of read/write (from the palette interface FPGA) in my host-VI to write a value directly to a control on my FPGA VI, I get the error-61499

The error occurs in the VI on my Hostcomputer ad message is:

An internal software error on the LabView FPGA Module has occurred. Please contact technical support.

The error doesn't happen, if I remove the read/write control, or if I do not speak.

The error does not happen, if I compile the fpga vi and let it run on my fpga hardware. It only happens in simulation mode.

The error mode simulated when I use the test bench to simulate the input signals, she also happnes, when I use random input signals.

It seems that the error does not occur when compiling. The slopes of simulated VI and the error occurs only when I call the read/write control.

Can someone help me?

I appreciate any suggestions

Thank you

David

OK, the problem is solved, thanks to the support of or who helped me:

The solution is, do not to have spaces and end of lines in the names of items frontpannel.

In simulation mode, a host vi has problems to access the elements of the frontpannel of the fpga vi with the read/write node if the façade elements have special characters.

-

Running in emulation in Labview FPGA VI 2009 Mode

Hello

How can I run the FPGA VI in Labview 2009 emulation mode so that I can run VI FPGA before compiling?

Thank you and best regards,

Rashid

Hello r,.

You have a 5640R or another card based R-series? I'm going to assume your VI FPGA makes equipment to a 5640R calls due to the

Forum in which you've posted. If this is the case, because of the architecture of

Screw model, the emulation mode is not supported in NOR-5640R. If you want to

emulate your logic and no appeal of material, it is possible, but it can also be

fact in a host of vi. -

My program has normally run this afternoon, but after I saved the new file (seems no change), I can no longer see the wave in the wave chart more at the launch of the vi of the host. Only when I keep the FPGA vi running can the wave be displayed on the chart. I don't understand what happened. I used Run like the invode method but I can't browse FPGA vi host more. Any help will be much appreciated. I've also attached the FPGA and host vi, which is barely changed from the examples.

You have no need to run it invoke the method as your open FPGA VI reference is currently configured to automatically run the VI. I recommend you either remove the invoke method or right-click of your FPGA VI reference open and change its options so that it is not automatically run.

The way you transfer your data between your FPGA and host VI could be the problem. Currently on your FPGA VI, you have a waveform chart and a function of bundle. As a general rule, you don't want no graphics on an FPGA VI front, since it is as just the low-level code do your FPGA-level tasks. Display you your data when you pass it to your host. In addition, there is no reason to combine a single item of data in a cluster, you can just do an indicator I16.

In addition, I do not understand the system calendar, maybe I'm just confused here. Your front panel for loop rate default configures the FPGA VI to enter a new sample of AI every 100uS. Which means the FPGA will be claiming a break 10,000 times per second. You have your host VI set up to wait for a break before the reading of the indicator, but the host is configured to run every 10ms, or 100 times per second. Basically you have your FPGA and your host VI running at different rates orders of magnitude, but try to synchronize the bed with an interruption.

You can run the FPGA and host screw at different rates with success using a FIFO of DMA or a queue, between them. Ensure your FPGA VI is grabbing samples very fast and packing in a queue, one both for the host VI to grab a chunk of at a slower interval. There is a great document on how to do it here: http://zone.ni.com/devzone/cda/tut/p/id/4534

-

Run code on the host target RT and FPGA

Hi all

I'm sorry if I ask a question to repeat. I searched for this a bit and couldn't find a solution.

I'm trying to run a single VI (be it on RT compactRIO or on the connected host PC) and enforce the code on the host PC and target the FPGA code RT. I currently code that runs on the host PC computer that opens the FPGA reference and executes code FPGA, but I don't know how to do this with a VI on the target of RT. Any advice/help would be great. Thank you!

Brandon

You are not far from your goal. But you need to at least

- Update FPGA code (Bitfile) containing your code to run on the FPGA.

- An executable compiled for your goal of RT, which is set to autostart.

You can use the code from my first post as a starting point. Compile, deploy and set it to autostart on your target of RT. - An executable compiled for the host machine. that your user will begin.

You can use the code in my first post, maybe load IP address, Port etc. of the Ini file settings.

If you double-click on the exe file on your host computer it will open an application reference to your target computer of RT and call the VI on the target machine. This is how you run code on your RT. From this RT code you can download and run the FPGA (bitfile) to your FPGA code or control which is already running the FPGA by controlling a state machine code. Load more screws to your memory of RT targets and call them from your host to add more functionality if you need to.

-

Broken the FPGA VI but the empty error list

Hello!

I'm trying to run a vi which includes a 'Open FPGA VI Référence' function. However, an error and it says that "not compiled FPGA VI. When I try to compile the FPGA VI a message saying "The VI is broken". I try to run the FPGA and when appears in the error list, there is no error or warning in the list, although the name on the fpga includes the Red 'X' ('show warnings' is checked). Any help?

I'm using Labview 2013.

Pablo

Hi Pablo.

Sorry for my delay in responding, you managed to get the respected FPGA.vi yet?

To answer your questions, if the project is ok with an empty FPGA.vi, then in theory, your hardware is configured ok. However, due to the vi being blank, you haven't tried to use one of the modules on your system, so it can introduce errors. The most common mistake is differentiation of mode Scan Mode/FPGA by installing the project in the first place. Also be aware that not all FPGA targets supports everything, for example some dislike for the rows that have an index to calculate the number of iterations, rather than a constant wired at the entrance to "n".

Out of curiosity, why you place every measure in the DMA separately and also specify address? Is there a reason you don't just place all the measures in a table and put everything in the DMA, then divide the table on the other side?

Generally speaking I don't think that incorrect programming should never cause LabVIEW crashing and you should always report the problem to the OR in order to take a look and see if they can fix it.

Hope that you managed to get your problem sorted and again sorry for the late reply.

Darren.

-

Why get error during execution the FPGA VI?

Hello world

I have a lot of sense of wrong during execution of a program that has been correctly executed previously. I don't know what I did wrong.

Now, whenever I run this FPGA VI, I get an error (in the attachment). And, then runs the FPGA VI, but it does not give the data required those he supposed to give as output.

Any help or recommendations would be appreciated also.

Thank you.

Hi auree123,

There are a few reasons for this error

may occur. Could you tell us more about what's going on?You are

I get this error when you compile and if so, at what stage?It looks like

as you may be running it in Interactive Mode, which means that you are viewing

the front of the FPGA VI on the development computer that you are running - is

that correct? If so, you could try to create a VI on your host

Open a FPGA reference and communicate with the FPGA programmatically rather than interactively.Thank you

Morgan S

Technical sales engineer

-

Hello!

It's running the FPGA VI.

I would just ask you what is the likely cause of the FPGA VI out of different answers every time that I run it (as I'm not closing the VI or change anything in the FPGA VI, I just "re-run").

Thank you!

Hello!

I already solved the problem. I used an other VI to reset (call the method).

Thank you.

-

Chassis FPGA deployment problem

Hello!

I use cRIO 9024 with a voice coil actuator control modules.

The problem I have is that when I run the FPGA code, he said "the chassis is in programming mode Interface to Scan. In order to run the FPGA screws, you must go to the property page of the chassis, select the FPGA programming mode and deploy settings. »

So I checked the property, but it has been defined as "FPGA programming Mode. Also when I'm trying to deploy the chassis, I have error message "LabVIEW: (Hex 0x80DF0010) current deployment operation has a missing dependency."

Since I'm not the one who wrote the code, I have no idea what causes this problem. This code is used for the different game with the same model of cRIO but different modules. I've already replaced modules that I use with those that are necessary for this code.

Anyone know what is happening here, please?

Thanks in advance to 1 million.

Geehoon

-

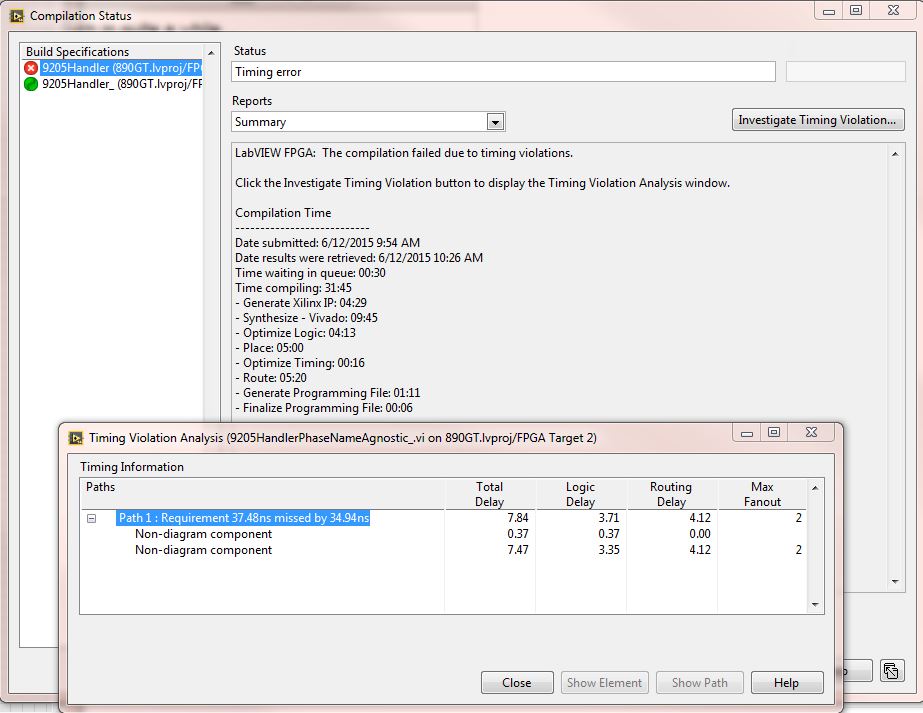

FPGA: update w / 14,4, fails w / Vivado 2013.4

My FPGA code that compiled fine in LV 2011, then 2013 LV (using Xilinx 14.4). I didn't contact for some time...

The upgrade to SP1 2014 LV, I believe that I have to re - compile to get the bit file to run on the target of the cRIO. However, now it does not compile. Cloud compiler error of timing. Clouds (local and compiler and elsewhere) report using Vivado 2013.4

The code handles a moudle of analog input of series C 9205. 6 of the 32 channels are run by a calculation of RMS. A time loop is set to do this each 185 uSec (9205 card channels = minimum update 4uSec * 32 channels = 128uS = maximum theoretical to run the FPGA and to obtain valid data). Each value of 650 samples a new RMS is calculated.

The rest of the channels get on average, 8 samples are averaged every 100th iteration of the loop above.

The timing of the loop is a front panel control. I tried this increasing by 185 to 200 uSec, but it does not help. All inputs and outputs to the FPGA VI are written in / reading of the *(cRIO-9068) of host real time be using the controls on the front panel.

This code has not changed in a very long time. I could share it if it helps.

My questions around the investigate Center window timing results. Here, nothing seems useful. What is "path 1' and how is it related to the block diagram? View items and path are inhibited. I have tried to change the build - optimize the performance and optimize for area etc... but the compilation always fails.

I will create a ticket with NEITHER. But thought pehaps someone here might have additional guidance.

For applications using hybrid...

(1) update install to 14.5 CompactRIO: C Series Module Support 14.6

(2) change of generation to optimize performance

-

When I try to create an executable from a host VI that has an "Open FPGA VI" reference who has run, the value "Dev computer w / Sim i/o" value, the application is built without error but when I try to run it, it opens with an arrow broken to run and has the following error:

"VI has an error of type 2302200. The full development of LabVIEW version is necessary to correct mistakes. "In fact, he repeats this message two times in the same window for some reason any.

Moreover, I * have the LabVIEW full development version and I use 2010 SP1

While the error message is not as clear as it could be, you're right: you cannot run an executable file that tries to run an FPGA VI in the simulation. It would be nice if there was an error in compiling. I always forget to switch to run on the target FPGA before building my application and discover the error until I have it copied on the system in the laboratory.

-

Embedded FPGA vi - network shared variable not updated

Hello

I work with an ethernet RIO 9149 of data acquisition. I use a hybrid programming mode.

I have a very simple FPGA VI that I downloaded on the flash memory. I used the indicator led to show my VI runs once the power of the RIO. Everything is fine, except that my shared network variables are not updated in the DSM ("no known values" displayed). However when I run the FPGA VI of my laptop, only once then stop and close (with 'interactive execution'), then my shared variables are updated in the DSM.

Any ideas why is this and how do I get the RIO update automatically shared variables without having to run the VI once?

Thank you very much.

Hello

I did a few tests and research and discovered that it doesn't seem to be possible. It is important to note the difference between Network-Published static (NSPV) and Variables of e/s of Network-Published.

The other are "user defined variable I/O" to communicate between FPGA and RT (RT absent on chassis Ethernet as the NI 9149) host. If these variables are checked to be published-network (in properties). They are accessible by VI running on the hosts of the same LabVIEW project, so you need to run a VI to access, as you mention. This is explained on the next page, Variable IO data custom FPGA of e/s (real-time Module or Module FPGA):

https://zone.NI.com/reference/en-XX/help/371361H-01/lvioscanhelp/io_vars/#user_IOV

I did find a way without a host (host RT or Windows PC) running a VI. If you have a cRIO with RT and NPSV host in the RT VI it is possible.

-

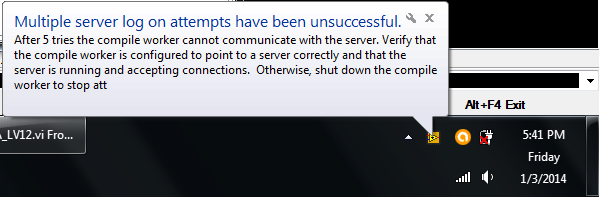

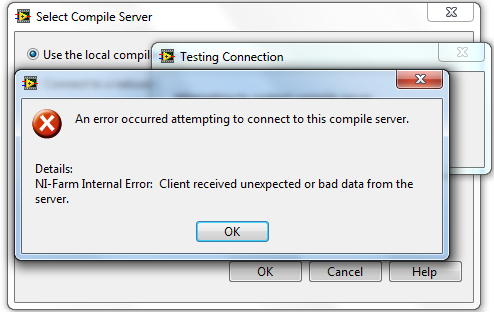

Internal error OR-farm - impossible to compile the FPGA VI

Hello!

When I try to compile any FPGA VI with LabVIEW2013 or 2012 SP1, I get the following error:

"Year error occurred trying to connect to this server compilation."

Details:

Internal error OR the farm: Client Server received unexpected or bad data. »

Intermediate files are not generated, the error message appears immediately after I have select build of build specification or I click the run arrow.

I use the local server for compilation.

The equipment I use: CompactRIO Evaluation Board - SbRIO9636, DELL laptop, Intel core2 Duo T5800, 2 GHz, 3 GB RAM, Windows 7 Ultimate 64-bit, SP1.

The intermediate files CAN be generated without any problems if I select in the menu. If I run the FPGA application compile worker, a ToolTip message specifying that "FPGA compile runs", but after a few seconds, another message appears: newspaper several attempts were unsuccessful - please see attached images.

At first, I thought that my firewall (Comodo 6.3) is the reason for this, so I disabled it but nothing changed. Then I tried to fix LabVIEW FPGA and XILINX tools with the firewall disabled but din do not solve the problem. I tried with LabVIEW SP1 of 2012 and 2013.

If you have any suggestions, please let me know! Thank you!

We would like that you try to reset the NIAuth database by following these steps:

1. go to Windows Services (Bring up Windows with Ctrl + Alt + Delete Task Manager, click the Services tab, click the Services button at the bottom right of the window.

2 stop the NI Application Web Server and NI System Web Server services in this order (right click, stopping service and select).

2 backup, and then delete all the files under %PROGRAMDATA%\National Instruments\NIAuth: registry.bin and commitmark.

3. run NI System Web Server and NI Application Web Server services in this order.

4. navigate to http://localhost:3580 / connection of an IE on the local computer and try to log in with username "admin" and password empty. Succeeds, the server will return one signed in as: message from the admin.

After you follow these steps, try and connect to the FPGA compiler, and then let me know what are the results.

-

Rinse the target DMA to host FIFO FPGA

I have a program that runs on FPGA waiting for a ppr pulse 1 a coder, then begins to acquire data based on 4096 pulses of ppr. After that it becomes 4096 pulses, it synchronizes the back upward with the pulse of 1 ppr and recidivism. If the encoder stops spinning in the middle of a revolution, I have a timeout will happen, shouldn't get a pulse of 4096 in some time. This way my code isn't stuck wait pulses if the encoder stops turning. Then, it warns the user and synchronizes backup with the pulse of 1 ppr when spinning resumes.

Well, the encoder stops at Midway through a revolution of spinning, I get a timeout, but now there are 2048 (4096 ppr * 0.5 revolutions) stale data points in the FIFO. I want to get rid of these points so that once it syncs back upward with the pulse of 1 ppr, I have data in the FIFO, all of the current revolution. I guess I could take the timeout error and trigger a loop on the side of RT that removes the elements until the FIFO is empty, but if it is not in time, before the encoder starts to turn once again, I still stuck with stale data. Maybe I need some sort of handshake with controls? I could also put FIFO for target on the FPGA for storing data and not the tail it to go to the host until it is all there. If I get a timeout, I could please rinse on the FPGA FIFO, because there is a method for flushing to target FIFOs.

No matter which deals with this problem before, and how to solve?

Hello

I think that your first method is the best option. When you save a timeout, have triggered a case on your side of RT first making a FIFO reading which returns the number of items in the FIFO (but reads the items suck) and then immediately do a read FIFO that reads the number of items remaining. This will clear your FIFO and it should run quickly.

-

Several loops of RT; A single FPGA reference

I have three loops using the same reference FPGA.

Loop 1 - reads most of the data in the FPGA for display on the HMI

Loop 2 - using the information made available to the loop 1 as well as some additional data that is read from the FPGA to perform the functions required by the HMI controls and writes for the FPGA.

Loop 3 - uses data from Loop1 as well as additional data read the FPGA to run commands fuctions and wrote security for the FPGA.

My questions are:

The FPGA Refence points to a single memory block where all three loops are looking at the same data?

I need on While loops shift registers to keep data updated correctly?

I need to run the three sons reference FPGA close While loops to close the reference correctly?

Yes. N ° N °

I assume you mean wire reference FPGA entering a node that reads the FPGA reference you speak or write in the Panel control or indicator that is part of the VI running on FPGA.

Maybe you are looking for

-

MacBook pro takes more than a minute to start

My Macbook Pro takes more than a minute to start. I though it was normal, but I've seen Macbook Pro my friend and it only takes 15 seconds to start. How to improve the startup time of my Macbook?

-

Impossible to install the Toshiba multimedia center

I recently bought a Toshiba 5.1 Audio & LAN USB 2.0 hubs and I installed corretly material, but when I try to install multimedia center software Toshiba I get an error message: "Setup is unable to detect a product that is supported on your system. Pl

-

Liquid level, NI ELVIS II + and Labview

Hello I am currently using a Liquid level detector, what I can say, is that it has two States, the float down = closed Contact; More float = open Contact. I wonder how do I plug the map of elvis and view both States on labview. Sensor in question htt

-

Windows XP does not display the available wireless connections

I formatted my hard drive and created two partitions. Then I installed Windows XP in one of them and Vista in the other. Then only under Vista the network card works and I see all kinds of connections available. Where, in Win XP it will not display t

-

Update of PC Companion by mistake

Hello. I leave companion pc trying to update itself or I use installer smartphone that download the latest version, the software is TOTALLY Impossible to install the latest version. I always get stupid error that says that there is a fatal error duri