RT FIFO error

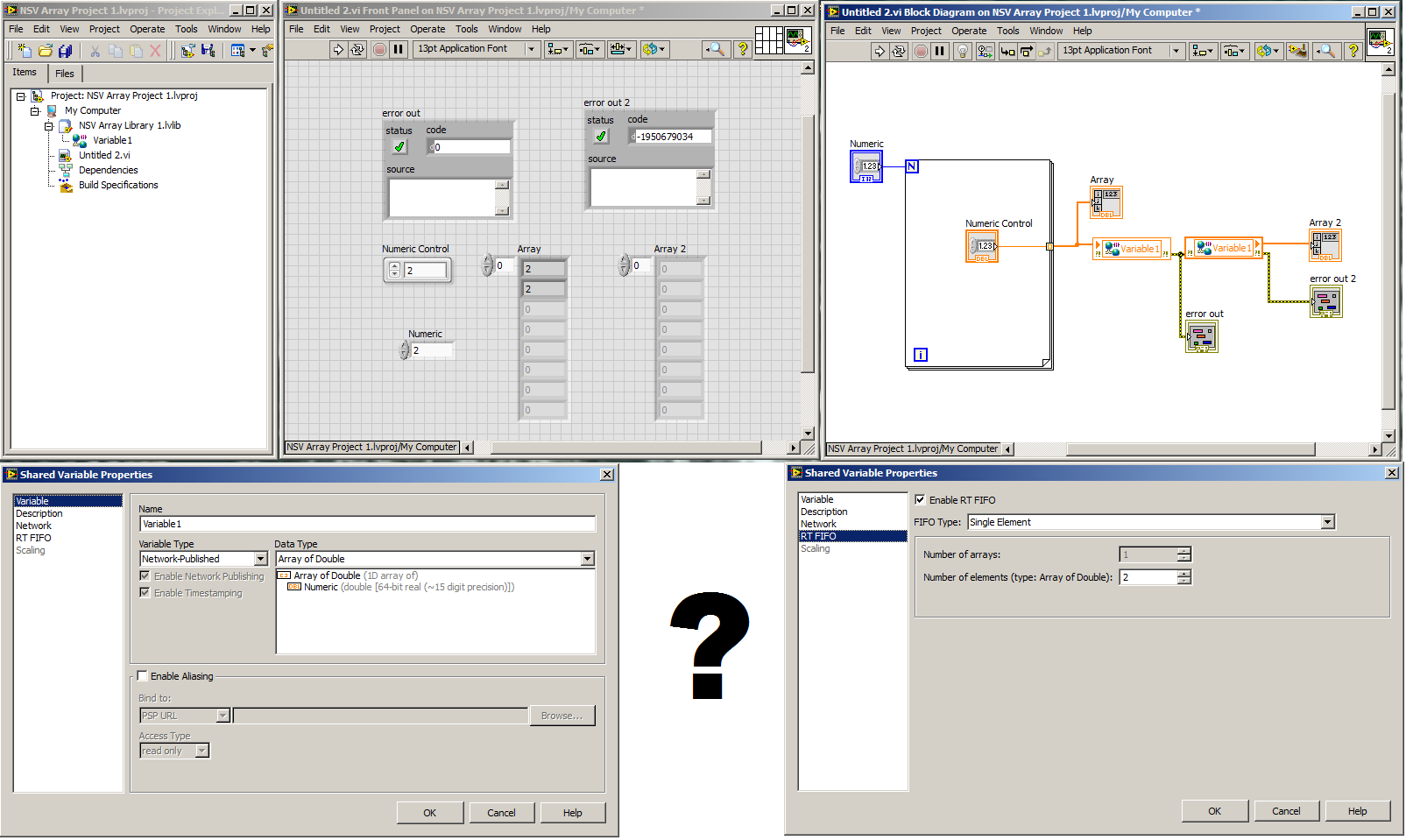

I have created a RT FIFO as in the figure below.

When I want to write about the FIFO, I get the following error.

Tags: NI Software

Similar Questions

-

Dear all,

I already configure switch Dell N3024P it pops up an error in the command line (CLI) like this:

<187>Mar 17 21:40:13 ARM_CORE_1 - 1 DRIVER [bcmDPC]: broad_hpc_drv.c (4428) 1169 %% unit: 0

CDC RX FIFO error table entry 0 19 ECCWhen I check in the internet there is someone said that there is an error of memory, - is it true?

And then how to fix the error?

Please please need your help.

Thanks before.

The firmware is applied to the stack master. The rest of the switches is synchronized to the master firmware version. But the whole stack will require a restart before the new image is active. Page 31 of this stacking guide goes into more details on the process.

-

I have 2 stacked N2048P switches. Shortly after the deployment, I started to have constantly the errors below:

DRIVER 172.x.1.x - 2 [108576100]: broad_hpc_drv.c (4362) 8073 %% unit: 0

CDC RX FIFO error table entry 0 39 ECCDRIVER 172.x.1.x - 2 [108576100]: broad_hpc_drv.c (4362) 8121 %% unit: 0

CDC RX FIFO entry error 37 double-bit ECCHere are the nine switches configured by Dell. I'm not familiar enough with the operating system to solve problems. Everyone knows this? If so, how to solve it?

Hi chanjohn01,

The error is a memory error. You can try to update or Flash the image and see if that helps. http://www.Dell.com/support/home/us/en/19/drivers/DriversDetails?driverId=Y7V3N&FILEID=3376784553&osCode=NAA&ProductCode=networking-N2000-Series&LanguageCode=en&CategoryID=NI

If this does not resolve the problem, try unstacking and ensuring that it is just the first member of battery that is giving the issue, the error refers to unit 0.

-

Hello

I see below errors when I run ' statistics of network adapter for the network esxcli is vmnic3 - n: on one of my server ESXi. "

nic # esxcli network statistics get vmnic1 - n

NIC statistics for vmnic1

Packets received: 53755035

Packets sent: 154420989

Bytes received: 8849592608

Bytes sent: 40797622427

Receive packets dropped: 0

Transmit packets dropped: 0

Total receive errors: 11503

Receive errors of length: 0

Receive errors: 152

Receive CRC errors: 11351

Receive frame errors: 0

Receive FIFO errors: 0

Receive errors missed: 0

Total transmit errors: 0

Transmit failed errors: 0

Transmit media errors: 0

Transmit FIFO errors: 0

Transmit pulse errors: 0

Transmit window errors: 0

I don't see that AD Server VM running on the ESXi VMXNET3 adapter on the virtual machine. "my track has started to broadcast alerts on these settings, but I don't find more information on" "Receive errors" or " Receive CRC errors"

anyone seen this issue or guide me on a KB where can I find more help.

Thank you

Praveen

There was a problem with the switch port of FI where I received the CRC package falls, we reset the port and these alerts have been arrested. but I don't know how can I reset the counter to ESXi end without having to restart the ESXi. anyone?

-

Passing an array via one RT FIFO network shared Variable, Code error-1950679034

This should be simple. I'm just passing through a table via a single RT FIFO network shared Variable element. And yet I get nothing. How could - not working? What is this error?

Well... it must have been some sort of thing calendar because adding an expectation of 100 ms fixed it straight up.

Now don't feel ridiculous

-

Reach target FIFO / missing error methods

In my project, there are two FPGA vi and 4 pairs (reading and writing) of FIFO extended target that are used to pass data between the two vi.

A vi FPGA (named rs232.vi) writes the data it obtains from a port RS232 to READ FIFO; also, it reads data ENTRY FIFO and transmits to the ports.

The second vi FPGA (named griffin commands.vi) writes data to WRITE FIFOs and reads data from READ FIFOs. There is no other vi in the project.

When I try to run either of the vi, I get an error about missing methods to FIFOs. For example, when I run rs232.vi, I get an error requiring a reading memory FIFO so that the read method (see the image named side rs232) and who should write FIFOs have Scripture metod presend on the vi block diagram. However, these 'missing' methods are present in the second FPGA (as I described above). The same type of error appears when I run the second.vi.

Why the compiler can't see I have all the methods; However, they are in 2 separate vi? How can I avoid this error?

SophieJS wrote:

Why is - a VI is not the top level vi?

It would be nice too, as long as one of them call each other. I don't see in your screenshot, however.

-

for the FPGA fifo compilation error

Hello

I downloaded the example RS232 FPGA program and tried to make a small change to it. The original is like that; See attached file "beforeModification.PNG".

I wanted to reread the amount of data still in the FIFO where I had read everything so I changed it to that. See attached file "withModification.PNG".

The target is using the compiler 13.4 Xilinx 7841R. I'm not in the section summary with the following error message;

Details:

ERROR: HDLCompiler:1566 - "C:\NIFPGA\jobs\K7I4YEj_RQC5mWo\NiFpgaAG_FPGA_Main.vhd" line 869: Expression has 11 elements; official ocountfullcount wait 10I'm currently running;

LabView 2012 SP1 f3

12.1, the R Series multifunction RIO of NOR

I'm doing something wrong?

Thank you

Andy

The problem disappeared when I copied the source files in a different folder

-

FPGA FIFO real-time error-61206

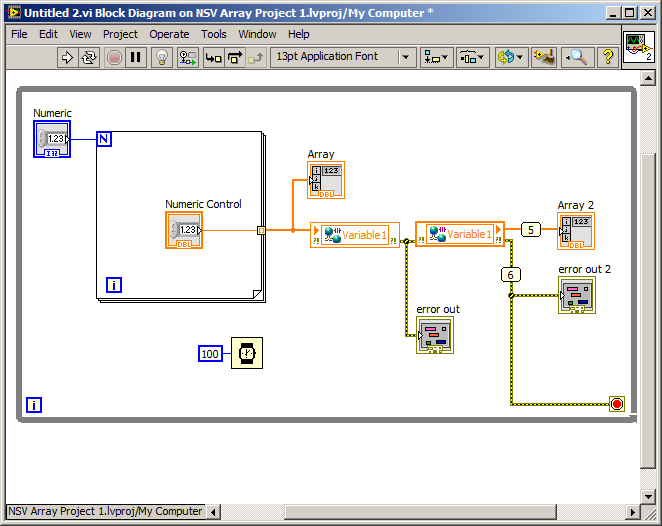

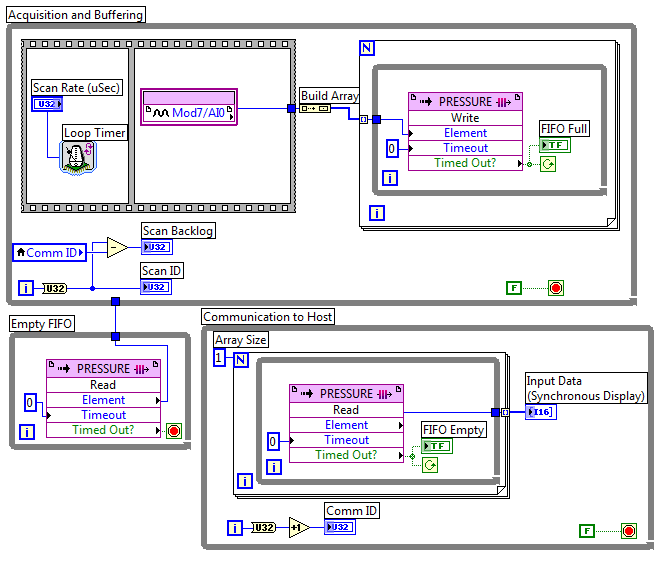

I used this white paper as a base for my code. My FPGA look like:

And my time real-time (RT):

I am using a cRIO-9022 and now just trying to get the foundations buried for my project. The problem is that the side FPGA works well but environmental RT takes maybe 2 or 3 seconds and close with this error:

Code:-61206

Source: Read/write in FIFO_pressure_RT.vi control

I have not dealt with the FIFOs in LabView before I have no idea what is the cause. Any ideas?

Thank you

Logan

What version of LabVIEW are you using? In LabVIEW 2011, if orders or the lights on the front of the FPGA had a jump of line or transport back in the label, the question would be filling in the read/write control node, but you would see this error. It seems that Input Data (synchronous display) probably has a newline character that could cause this. That the problem has been solved in LabVIEW 2011 SP1, but what happens if you remove the line break and recompile the FPGA VI?

-

Hello

I'm developing a program for the acquisition of data on a cRIO-9074. In my loop acquisitin of data on the target of RT, I saw a block that is then in a RT FIFO queue. It was working when I went into subtables block, one for each sample, but now I decided to use another while loop parallel to manipulate the data (using the function array decimate). When RT FIFO write trying to write the block to the queue, it throws an error with the code-2206 (which is not documented that I can tell), and the message says only that the error occurred in RT FIFO write.

If someone could help me with that, it would be greatly appreciated! Let me know if I should join the VI.

Thank you

Alex

G money

Thanks for the reply, but I thought about it. The RT FIFO was closed when it should not have been due to my inexperience in writing code with simultaneous loops. I just ran the code with the debugger on and saw the problem immediately. What a great tool!

Alex

-

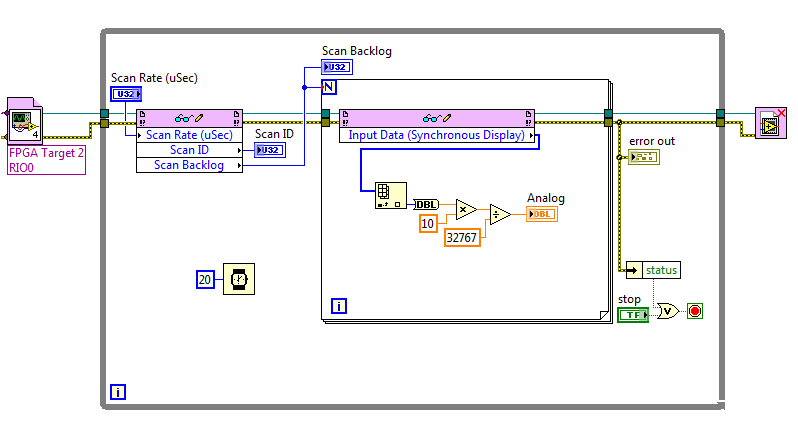

Error-50400 occurred to the Invoke method: FIFO. Read in Host.vi

Hey there,

We have sensors on an engine which are connected to a Board of Directors OR cRIO 9014 (with a NI9411 6 digital input modul channels) and from there, via the network to a host computer.

cRIO jury: the jury cRIO collects data from the engine and stores in a buffer, it's because the network is to slow for the size of the data

Host: bed of the host computer in the network buffer on the map of cRIO, on the host computer, it takes specific portions of the data to create charts of the engine pressure

Error:

Error-50400 occurred to the Invoke method: FIFO. Read in Host.vi

Possible reasons:

The transfer did not complete in the time-out or the specified number of retries.This error occurs in the following scenario:

-motor is running

-cRIO is running

When I press the Start button (boolean 3) in the host.VI to start reading the data of the card AFTER I pressed the button to run the host VI.

The error will not occur if I pressed the button start (3-Boolean) BEFORE I pressed the button to run the host VI.

We tried to increase the timeout, but it still does not work, the error occurs!

We would be really happy if you could look over it and help us in this case! If you need more information or if we need to clarify a specific part, please let us know!

We have included the VI in the attachment!

Thanks in advance!

CHRISSE,

There are a few things wrong in your application, if I can offer a few suggestions.

First of all, your loops are not running in parallel. In fact, they are in while loops with a real constant wired for them. I don't know if this is normal for debugging, or on accident. I would put the question (read pulling elements Dummies) out of your hand while loop.

Your second nested while that the loop (that of the poll the number of items and then shooting them) will execute only once and can make only a few samples. I don't think that that's what you're looking for here, and there are two ways we can go here. You might question continually until you have 0 items available for x time, then you know that you have no more available samples and you can process all the data, OR you can put your computer through this loop and always just write in the file immediately in the form x samples are drawn.

In addition, the stop of the main loop condition is ( <= 3)="" therefore,="" it="" will="" run="" once="" and="" then="" stop. ="" maybe="" you="" mean="">= 3?

In addition, you have "add to the file" disabled on your writing to the worksheet, so whenever you write that you are overwriting the old data. If you want to write constantly, you will lose data. This can be cured in this affecting true (requiring a new name for file or programmatically removing the old worksheet each time that you run the vi) OR you can recover all your data in a shift register and only write to the file once you have all your available data.

The error you see is because you try to close your FPGA reference twice. Simply close it once.

After seeing your overview, I think this can be cured by simply reading wiring to get your 1440 X 4 items, but as we have seen, this does not work. Something happens in your system... that's what I want you do... just run the following... code and let me know how much remaining elements it gives you... Once the number remains (I hope for this, and your engine continue to function), press stop, and all values will be presented on a graph for you. My broken wires are because I do not have the FPGA VI.

-

DMA FIFO of FPGA compilation error

Hello

I have a cRIO 9074 with FPGA. I tried a simple piece of code to learn how to acquire the data that is generated on the FPGA at a rate of 10 KHz and transfer it to the host VI to treat later in offline mode. However, I meet this compilation error when you compile the FPGA VI base containing a node to write FIFO (photo of the VI attached below). In compiling the report, it is said that there are 256 RAM Block used (the total number is 40), so an error has occurred. The error notification of exact compilation from Xilinx report is reproduced below:

# From the PAM program

# o toplevel_gen_map.ncd - intstyle xflow-calendar toplevel_gen.ngd map

toplevel_gen. FCP

#----------------------------------------------#

"Target part using" 3s2000fg456-4 ".

Design of mapping in the lut...

Guided running of packaging...

Running based on the delay of packaging of LUT...

ERROR

ack:2310 - type compositions "RAMB16" too found to adapt to this device.

ack:2310 - type compositions "RAMB16" too found to adapt to this device.ERROR: card: 115 - the design is too large to fit the device. Please consult the Design summary section to see what resource requirements for your design exceeds the resources available in the device. Note that the number of slices don't notice it that their packaging could not be completed accurately.

NOTE: A file NCD will be always generated to allow you to examine the mapped design. This file is intended for evaluation use only and will not be processed successfully by means of BY.

Mapping performed.

See the report of map file "toplevel_gen_map.mrp" for more details.

Problem encountered during the packaging phase.

Summary of design

--------------

Error number: 2

Number of warnings: 125

ERROR: Xflow - card program returned the error 2 code. Aborting the workflow execution...

Bitstream not created

Time history analysis

What does that mean? How can I fix this error?

Thank you

Bogdan

Hey,.

Have you already tried to reduce the size of the FIFO memory?

Christian

-

FIFO.config - 61206: but the name of the FIFO is

Hallo,

I am relative new to cRIO and I became a mistake the last time, I've compiled my FPGA.

Description of HW

- cRIO-9035

- 4 x NI9229

Description of the software

- FPGA: I have 15 DMA FIFO (I can do this according to this document), which send asynchronous messages on each FIFO (see the joint photo)

- RT: I get this message and I store them in a PDM file

Problem

- FIFO. Configure or FIFO.start gives me "error-61206." This error, as shown here, means that there is no such thing as the name of the FIFO. But as pictured there. I don't know what happened. Is the first time I get an error like this.

For your impeccable support, I'll tell you ' thanks!

Carmine

I found the problem.

Only really used FIFOs on FPGA can be configured.

If you declare a FIFO and you won't use it on FPGA (for example to do a test of part of your project) you need to remove from code RT parts where you configure, start closed ancd FIFO.

Thank your for your attention.

Carmine

-

Compilation failed due to an error of Xilinx.

I've recently updated since LV2014 until 2015, and an FPGA VI who previously compiled successfully is no longer made. My goal is a 7951R and I use a module e/s of 6584. A few minutes in the compilation process, I get the below error. I found the White Book of OR describing this problem for 2010 and provide a patch, but this solution has failed for me. Curiously, I can succeed in the compilation of FPGAS screws very simple, but not more complex that were previously viable.

LabVIEW FPGA: Compilation failed due to an error of Xilinx.

Details:

ERROR: HDLCompiler:432 - "C:\NIFPGA\jobs\ODf62Gx_H0cwa34\NiFpgaAG_0000023b_ForLoop.vhd" line 55: Formalhas no real or default value.

INFO: HDLCompiler:1408 - "C:\NIFPGA\jobs\ODf62Gx_H0cwa34\arrayLpIndx_593.vhd", line 22. array_in is declared here

ERROR: HDLCompiler:854 - "C:\NIFPGA\jobs\ODf62Gx_H0cwa34\NiFpgaAG_0000023b_ForLoop.vhd", line 24:Unit ignored due to previous errors.

File VHDL C:\NIFPGA\jobs\ODf62Gx_H0cwa34\NiFpgaAG_0000023b_ForLoop.vhd ignored errors

-->Total memory use is 239156 kilobytes

Number of errors: 2 (filtered 0)

Number of warnings: 11 (filtered 0)

Number of news: 0 (0 filtered)"Synthesize - XST" process failed

Compile time

---------------------------

Introduction date: 04/12/2015-16:36

Date recovered results: 04/12/2015-16:38

Waiting time in the queue: 00:09

Compilation of time: 01:44

-Generate a Xilinx IP: 00:00

-Estimate of the resources - PlanAhead: 00:33

-Summarize - XST: 00:56Okay, that was weird.

I discovered there was a small change between revisions. I had wrong initalized a table by exchanging the entries, so that the size of the array is 0 instead of n. normally, this should be taken at the beginning of the compilation, but this table null was used to initialize a shift register in a while loop and the exit from the while loop enters a loop, where my FIFOs operate. While the loop/shift register seems to be the essential element to the compilation of progress as he did and present it as a mistake of Xilinx. If you delete the while loop then the error is detected quickly and correctly identified.

-

buffering overflow of FIFO County edge even at very low rates

Dear Forum,

I try to use a PXI-6608 timestamp clock of a PXI-4498 for the analog input sampling. Because the sampling frequency will be the order of 20 KHz, I want to use a task of impulse generation on a counter to divide down by a factor of 1000, then use this pulse the door and the clock 10 MHz on the 6608 as source contour buffer - I wait about 20 edges per second, which should be handy to collect more DMA.

The result is that I get the error-200279 ("attempt to read samples is no longer available") immediately after the beginning of the vi, before that I extracted an indictment.

This is my first shot of dagger to using DAQmx for counters/timers rather than the old drivers for data acquisition, so I do not know I did something wrong, but I can't understand that.

I have attached the vi if that helps.

Thank you!

Case No.

It seems that you have your door and source to the rear. The sample clock should be ctr0internaloutput and the Terminal count edges should be 10 MHz clock. You get the buffer overflow error because the FIFO on the map is only 2 samples and 10 MHz, these are rewritten was faster that a computer could possible pull out of the map.

-

Error 50400 FlexRIO example "Coprocessor FFT"

As the title says, I have tried to run the example "FFT co-processor" located in LabVIEW 2013 FlexRIO PXI-7954R FPGA with examples but kept "ERROR-50400 occurred to the Invoke method: FIFO.» Write in TNI .vi co-processor (host). Possible reasons: the transfer has not completed within the time or in the specific number of retries. ».

I use LabVIEW 2013 SP1 with Xilinx 14.4 of the compiler. I didn't modify the code except copied the FPGA vi to the PXI-7954R target newly added and recompiled; and change the FPGA VI reference in the host vi as a result.

I tested the code in simulation mode (i.e., run VI FPGA on development with simulated IO computer) and it worked fine. However, when running on the target FPGA it does not work. I followed the 'empty remaining items' on "host-to - FPGA.Write" at the host vi and the value was 5. And "other" in "FPGA-to - Host.Read" in the host vi is 0.

It has something to do with the FIFO buffer size? Suggestions or comments are greatly appreciated.

Thank you

Bing

Theres a race condition in the code of the host. If you try to read before you write, then the FIFO is to expire. If you make sure that you write before you read while the timeout never occurs.

Attached is a version of the host code that writes then reads using a state machine.

Maybe you are looking for

-

MacBook Air does not illuminate

SO this is what happened: the night before my laptop was working fine. The battery at the time was about 20%. I turned off. The next morning I tried to turn it on, but she didn't only turn on. I tried to plug my charger but the "light" is not getting

-

Sites Web open automatically to the address bar.

When I choose a site to go to the drop down address bar menu, it does not automatically go to this site as it used to. I have to click on the little arrow to 'go to this address' or press ENTER. As far as I'm aware, FF hasn't updated recently, and it

-

Firefox does not open a new window

Firefox is a lot of time to open a new window. whenever I want to open a new window of cmd + n or file > new firefox waiting window two minutes before opening... I'm under firefox 3.6.3 on a mac book pro + leopard up-to-date.but when I try to open a

-

I can't get my Epson BX535WD printer to scan to the computer.

My computer printing fine and doing everything as it should, but I can't scan to computer.

-

I am trying to extract a zip file I downloaded, but the option extract is no longer there. I did so many times in the past with no problems. The icon is also different, where it helps to have a folder with a zipper, it is now a white square with a