Xilinx 10.1 vs 11.5 LabVIEW FPGA 2010

I use a target of the PXI-7853R FPGA, PXI-8186 controller runs LabVIEW Real-time and LabVIEW 2010. There seems to be a problem with the compilation of the FPGA code. Without going into details, like others within the company have taken this path without success, I have another path I want to test.

LabVIEW 2010 uses by default the compiler xilinx 11.5. Is there a way to say, strength, LabVIEW 2010 use xilink 10.1 rather than the 11.5 (old and new compiler) compiling? I have no need a why are you doing this response. I want to test to see if there is something with the new compiler who asks the questions.

Thanks for any help,

Bill

Hey Bill,.

LV 2010 do not by default Compilation 11.5 tools, depends on the FPGA using.

The 7853R uses a V Virtex leading using the tools of 11.5. The 10.1 will only be used if the target is an FPGA Virtex II FPGA.

Christian

Tags: NI Software

Similar Questions

-

Zip file and iso LabVIEW FPGA Xilinx tools 12.4 Module is broken

I downloaded the two zip file of LabVIEW FPGA Module Xilinx tools 12.4 and iso image file three times to make sure that both files are broken and can not be installed!

The size of the file is so large about 3g. It would be better to double-check before you download on the Web site.

-Very well,.

The download is complete and the standard Windows Extraction tool worked, WinRAR worked and 7Zip worked (and no, I don't know why, I installed all). I did download a wireless network that does not have direct access to our internal servers, it should therefore be a test valid. If the link I provided above was not that you used (probably isn't, because it is not an ISO option), could you please provide me with a link to the page that you used so that I can test and repair? In the meantime, the link above should work for you.

-

Drivers Xilinx/Multisim and Labview FPGA

Where can I find drivers for my FPGA OR if I use Multisim/Xilinx and NOT of Labview? All the links I found are Labview be installed. However, the explicit manual FPGA indicates that you can use Multisim/XIlinx ISE in place.

OK, I tested just outside. The Driver of LabVIEW 2013 DEFB contains 2 separate components, the driver and Module FPGA support. If you run this installer, it won't check if you have LabVIEW FPGA installed unless you check the box for LabVIEW FPGA support.

I can change the text in the Installation Instructions to read "LabVIEW FPGA 2013 is required to install the LabVIEW FPGA Module Support component installation".

-

Download NI LabVIEW FPGA Module Xilinx Tools 10.1 2013 problems

I'm trying to download the Xilinx tools 10.1 to use with a chassis 9113 in LV2011. Based on this white paper, that the compiler below should work perfectly. The problem is that I can't seem to download all the way.

I can't seem to cross ~ 336MB using the standard or the downloader OR. Any ideas? Does anyone else have this problem?

http://www.NI.com/download/LabVIEW-FPGA-Module-2013/4249/en/

Thank you

-PBD

Well well... on the good side of things, you don't want 10.1 anyway!

Virtex-5 LX50 FPGA<- requires xilinx="">

10.1 is only for devices FPGA Virtex-II! (.. .after LabVIEW 2009 it was, just for all of you who read this know).

so... try this link: http://www.ni.com/download/labview-fpga-module-2013/4248/en/

-

Hi all

I'm new to fpga and my question is fairly simple which is best?

LabVIEW fpga and xilinx ise platform?

or does rely on demand?

I'm not familiar with these protocols, so I can't answer the question precisely.

NOR has several FPGA products with high-capacity chips. I guess that they could manage the protocols, but I can't make any promises.

Unless you're already an expert ise, I don't think you're going to end up with a more effective than LabVIEW code. I guess that's a possible higher capacity chips are available for ise as LabVIEW, but I don't know.

One thing I like LabVIEW is that you can write the code and compile it for the target without having to purchase the equipment first. You could program the algorithm, and then understand what size FPGA, you put on.

Bruce

-

Please help me for this problem "error starting compile step: make sure that a compatible version of Xilinx tools is installed in the location specified in the setup of LabVIEW FPGA.»

Look for the error on the Web site of or or on the forums. Take a look at the following links:

http://forums.NI.com/NI/board/message?board.ID=170&message.ID=381394&requireLogin=false

http://forums.NI.com/NI/board/message?board.ID=170&message.ID=205754&requireLogin=false

-

LabVIEW FPGA Xilinx tool claims his license has expired.

I recorded the two & Labview Labview FPGA on my PC and the PXI chassis.

However, when I try to compile my code, I get this error message:

ERROR: Xst:1531 - for this trial software evaluation period has expired.

According to the agreement of the assessment, which has been shipped to you

as well as the trial CD, this software will be is more exploited.

We look forward to help you as you make your assessment of the Xilinx

solution. Your sales engineer local domain or the seller is available

for any questions or help you in the purchase of an annual plant

software license. You can also contact Xilinx directly at [email protected]

Thank you for the assessment of the solution of Xilinx. Thank you for your interest for

Xilinx and look forward to earning your trust and your business.

ERROR: Xflow - program xst returned error code 1. Aborting the workflow execution...I didn't think I need to buy something more in addition to Labview FPGA. Is this a bug?

-

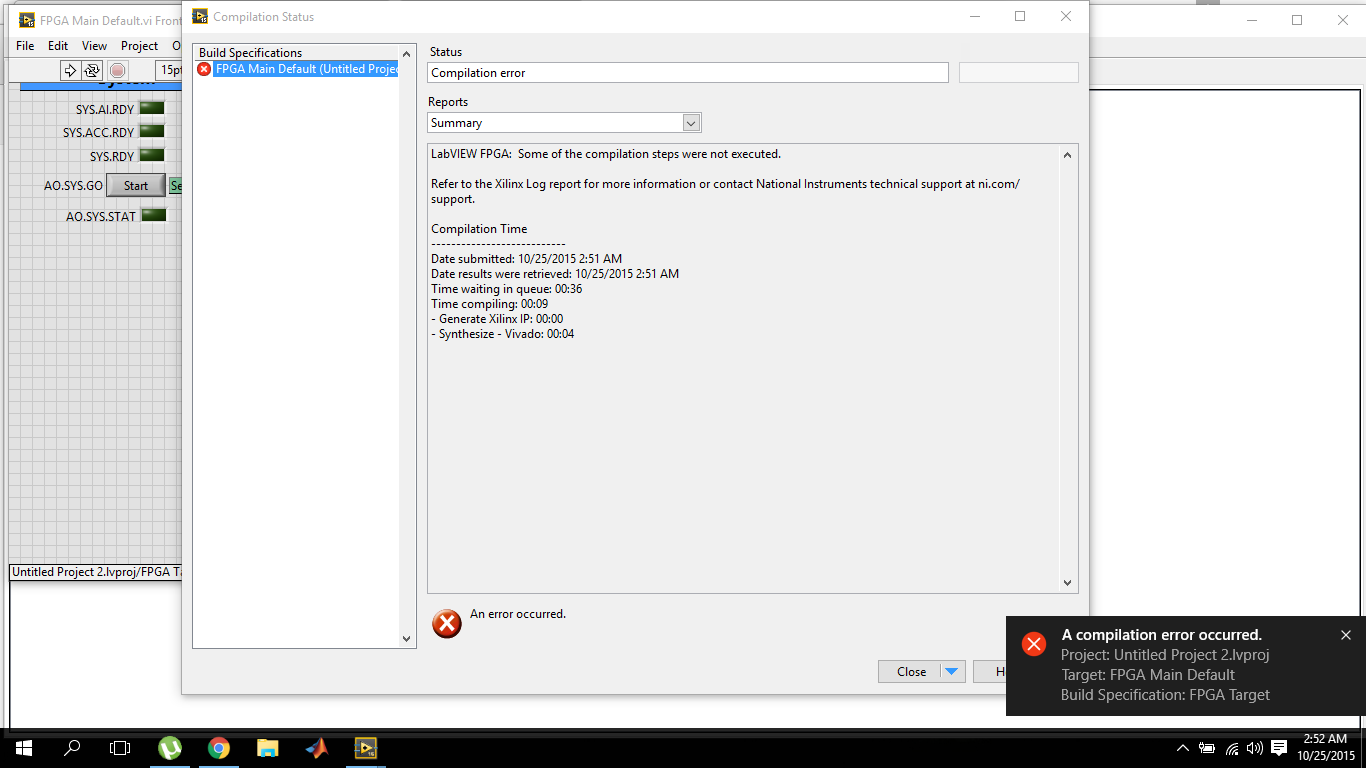

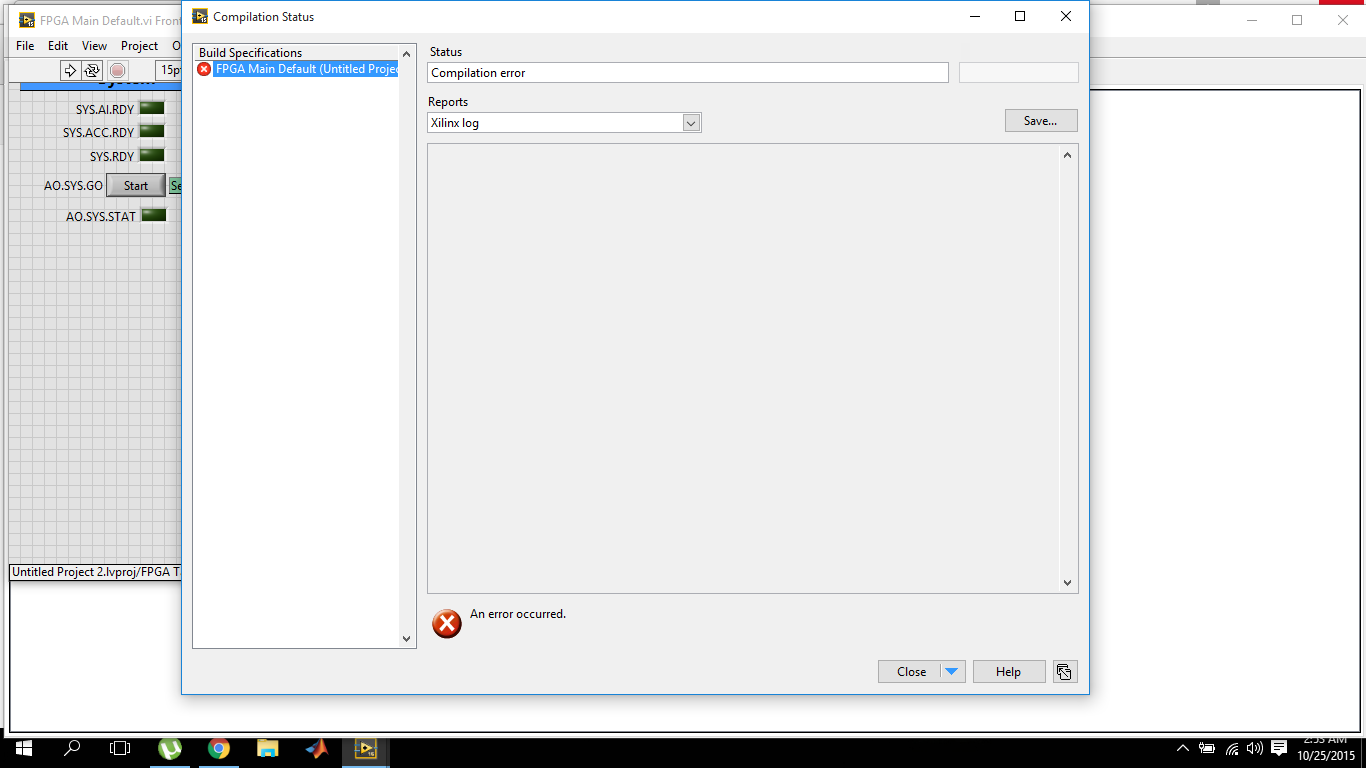

LabVIEW FPGA, 2015 compilation error

I've recently switched to LabVIEW 2015 and I'm working on OR myRIO. So also installed myRIO 2015 bundled software. The problem I have is that the compilation of fpga fails within 10 seconds.

and the target Xilinx journal report is empty

The first time when I tried to compile on 2015 version, it failed and the message box that failed came alongwith the avast antivirus warning for malicious activity. I reported it as wrong and now I tried several times with avast shield disabled control, but the results are the same. While the version of labVIEW 2014 works very well.

Now, I'm sure that there is something wrong with the installation of Vivado because this dll is part of it. The dll must be default in the2014_4\lib\win32.o directory C:\NIFPGA\programs\Vivado if you are using an operating system for 32-bit AND also in C:\NIFPGA\programs\Vivado2014_4\lib\win64.o If you use a 64-bit operating system. If the dll is not here, it is probably that the anti virus (I've never seen what happens to Xilinx but I have for other stuff).

I'm emphasizing the 2014_4 because LabVIEW 2015 uses Vivado 2014_4 while 2014 LabVIEW uses Vivado 2013_4. Since you have also installed LabVIEW 2014, you must have 2013_4 as well and if it works, you will find the dll I just wanted you make sure you check the correct directory for the Vivado 2014_4.

Download and install (reinstall or repair if already installed) 2015 LabVIEW FPGA Module Xilinx tools Vivado 2014.4. You can also use the DVD Setup if you have. It would be a good idea to do the installation with the disabled and even anti-virus try the first compilation the same. Try and let me know if the problem persists.

Kind regards

-

Choose ISE or Vivado Xilinx tools for a specific compilation of FPGA

Hello

Is there a way to specify what version of Xilinx Compilation tools to use when compiling an FPGA VI? I want to try the version Vivado tools rather than the version of ISE to see if there is an improvement. I have listed some information on my setup below.

It's my current setup:

NI5772 / PXIe7966 digitizer and FPGA

SMU-1082 chassis

SMU-PCIe8388 / SMU-PCIe8389 controller

LabVIEW 2014In the past, I used the LabVIEW 2014 FPGA Xilinx tools 14.7 Module to compile my code. But I also want to try the version of Vivado, "LabVIEW FPGA Module Xilinx tools Vivado 2013.4 2014', to see if it gives better results."

Page-based "compatibility between tools Compilation of Xilinx and FPGA hardware OR" here:

http://www.NI.com/product-documentation/53056/en/

Looks like the PXIe7966 FPGA must be compatible with the tools of Vivado 2013.4.I tried to uninstall the version 14.7 ISE tools, and install the 2013.4 of tools Vivado (so Vivado 2013.4 tools are the only xilinx tools installed on the computer). But LabVIEW complains that the ISE 14.7 tools are not installed and does not compile the FPGA VI.

Thank you!

MichaelThis FPGA is a Virtex-5 FPGA, so you're stuck with ISE. You need a card FPGA that either uses the architecting chip (I think it was only in cRIOs) or 7 Kintex to use the compiler to Vivado.

-

LabVIEW FPGA: Integration node clock wrong

Hello

I'm having some difficulties to understand how the clock is part of the node IP for LabVIEW FPGA and was hoping to get some advice.

What I try to do is to set up a digital logic circuit with a MUX feeding a parallel 8-bit shift register. I created the schema for this Xilinx ISE 12.4, put in place and can't seem to import the HDL code into an intellectual property node. When I run the VI, I am able to choose between the two entries for the MUX, load the output in the shift register, clearly the shift register and activate the CE.

My problem is that when I switch to the entrance of THIS, he should start 1 sec shift (Boolean true, SCR, High, what-have-you) in the registry once each clock period. Unfortunately, it instantly makes all 8 bits 1 s. I suspect it's a question of clock and here are some of the things I've tried:

-Specify the input clock while going through the process of configuring IP nodes.

-Adding an FPGA clock Constant as the timed loop.

-Remove the timed loop and just specifying the clock input (I'm not able to run the VI that I get an error that calls for a timed loop)

-Do not specify the clock to enter the Configuration of the IP node and wiring of the FPGA clock Constant to the clock input (I can't because the entry is generated as a Boolean).

-Remove an earlier version of the EC who had two entries up to a door and at ISE.

-Specify the CE in the process Configuration of the IP nodes.

-Not specify this in the process of setting up nodes IP and wiring it sperately.

-Various reconfigurations of the same thing that I don't remember.

I think I'm doing something wrong with the clock, and that's the problem I have. Previously, when I asked questions to the Board of Directors on the importation of ISE code in LabVIEW FPGA, a clock signal is not necessary and they advised me to just use a timed loop. Now, I need to use it but am unable to find an explanation online, as it is a node of intellectual property.

Any advice would be greatly appreciated, I'm working on a project that will require an understanding how to operate clocks the crux of intellectual property.

Thanks in advance,

Yusif Nurizade

P.S. I have attached my schematic ISE and the LabVIEW project with one of the incarnations of the VI. The site allow me to add as an attachment .vhd file, but if it would help I could just paste the body of the code VDHL so just let me know.

Hello Françoise,.

I spoke to the engineer OR this topic and it seems that it was sufficient to verify that your code works, by putting a wait function of 500 ms on the while loop to check that the registers responsible and clear. I'm glad that it worked very well!

-

Move from LabVIEW FPGA block of ram address to node CLIP?

Hello

I need to pass an index memory RAM of LabVIEW FPGA block to a CLIP node to the node CLIP to have access to the data in the BRAM. The node of the ELEMENT contains an IP address that we developed and the IP address is the use of Xilinx BRAM driver to access data. I guess that we need to move the physical address of the BRAM to the ELEMENT node.

Is this possible? If so, how? If this is not the case, what would be an alternative?

Thank you

Michel

If I understand you correctly, Yes, you should be able to use the memory block of the Xilinx pallet Builder in LabVIEW FPGA and in the loop of the single Cycle, connect the ports of this block signals CLIP exposed by the IP of your colleague. You may need to tweak/adapt some of the signals slightly to the LabVIEW data flow.

-

When I compile a labview fpga VI, (my version of labview fpga is 2014), I get the not found error Xilinx 10.1 build tools.

But for 2014 labview, version 14.7 Xilinx is the only compatible and that I installed. But it is still asking for Xilinx version 10.1. I tried both with configured CompactRIO and also a vi without hardware. The same is repeated each time.

What can be the problem? Please help me.

Elodie

What FPGA target do you use? I think for Virtex 2 target Xilinx 10.1 tools are used.

-

LabVIEW FPGA: Problem compiling look-up Table

Current versions of software:

LabVIEW 2014 SP1

LabVIEW FPGA 2014

Xilinx Vivado

I'm having a huge problem in trying to compile my LabVIEW FPGA code.

Some recall of the code:

It's all in a SCTL.

I am streaming in a FIFO DMA and comparing it with the values previously stored in the shift registers (which are initialized to 0 at the start of the loop) in the SCTL.

The results of the comparison are then piled into a U16 and loaded into a lookup table (I use the LUT - 1 d), and I'm so help this LUT to decide what value will be charged to travel to record for the next iteration of the loop, which, in any case, would be either the current values of the flow, or the post previous registry value.

(It's a triage loop)

I am able to run very well in simulation mode code, but when I try to compile, I get this error:

"The selected object has a built-in shift register that makes the output on a particular loop iteration correspond to the entries in the previous iteration."

Connect the outputs of the object directly to a minimum number of nodes of Feedback or uninitialized shift registers. You cannot connect the outputs to another object.

See using LabVIEW for more information on the objects with registers embedded offset. »

Someone at - it ideas why this happens, and what might be the possible solutions?

I'm tempted to break it down into separate loops, but I prefer not to because it is now a loop (and working in my simulation).

I found my problem.

Any time that a LUT is in a chain shift register, it cannot:

1. be part of a string of shift register that has a variable initialized

2. follow-up to no decisive structure, like a box structure.

I just moved the position of LUT and it works.

-

HELP - FPGA SPARTAN 3E-100 CP132 WORKS WITH LABVIEW FPGA?

HI EVERYONE, GET ON IM TRYING TO USE MY FPGA WITH LABVIEW, BUT I DO KNOW THAT IF ITS COMPATIBLE, I INSTALLED THE DRIVERS, MODULE FPGA AND LABVIEW 2012, IM USING WINDOWS 7 32 BIT, AND AFTER I COMPILED ITS SAYS:

LabVIEW FPGA called another software component, and the component returned the following error:

Error code:-310601

NOR-COBS: Impossible to detect the communication cable.

Check the communication cable is plugged into your computer and your target. Also, verify that the proper drivers are installed.Thank you.

=)

Hi dvaldez2.

LabVIEW FPGA offers no support for any material to third parties, other than the 3rd Spartan XUP Starter Kit. These are probably the drivers you downloaded.

http://digital.NI.com/express.nsf/bycode/Spartan3E?OpenDocument&lang=en&node=seminar_US

However, this driver supports only the Starter Kit Board itself (http://www.digilentinc.com/Products/Detail.cfm?NavPath=2, 400, 790 & Prod = S3EBOARD). You may not use the driver with any other Xilinx FPGAS.

I hope this helps.

-

LabVIEW FPGA failure with compiler Xlinx?

I'm in LabVIEW FPGA 8.6 with NOR-RIO 3.0.1 (to 8.6). When I compile a simple program, I get the notorious:

«Error starting compile step: make sure that a compatible version of Xilinx tools is installed in the location specified in the setup of LabVIEW FPGA.»

I checked the FPGA compile server and I ran the utility fixTlink.VI with no improvement. This produces two identical PC, neither one having a FPGA installed card.

Any ideas?

After further analysis, the problem was to be in our facility in LabVIEW FPGA 8.6. Using the correct Installer of NEITHER solved the problem.

This thread is now resolved.

Maybe you are looking for

-

Where to get the interface for 500 GB drive HARD USB3

The USB connector is damaged, one of the bent pins.It does not seem to have the expected SATA interface where I could use a different case. It seems the only way to power and the HARD drive inside the interface, with a Toshiba pcb which includes USB

-

Tecra A9: Can I let Malwarebytes 'remove' qsqlpwd.dll infected?

First of all, I'm confused about two forums of Tecra... This one:http://forums.computers.Toshiba-Europe.com/Forums/Forum.jspa?forumid=68 Other one:http://laptopforums.Toshiba.com/tshb/Board?Board.ID=brd_Tecra They both look like they are forums for T

-

Satellite A300 - Windows 7, causing overheating

Hey all,. I have an A300/y01 toshi (psagca - 02y010) and that you have recently upgraded to windows 7 64-bit, since the upgrade, I was unable to find a toshiba power saver, which is compatible with win 7, and my pc is a lot hotter then he did a few d

-

Virus detected... Is it true or BS?

I was browsing Safari when this happened. I think this is BS, but I wanted to get some other opinions. -

-

How to remove the CD from y550 4186

I need to remove the drive and replace it with a new one, but I do not have the removal instructions. Where can I learn how to do this?