LabVIEW fpga xilinx ise vs

Hi all

I'm new to fpga and my question is fairly simple which is best?

LabVIEW fpga and xilinx ise platform?

or does rely on demand?

I'm not familiar with these protocols, so I can't answer the question precisely.

NOR has several FPGA products with high-capacity chips. I guess that they could manage the protocols, but I can't make any promises.

Unless you're already an expert ise, I don't think you're going to end up with a more effective than LabVIEW code. I guess that's a possible higher capacity chips are available for ise as LabVIEW, but I don't know.

One thing I like LabVIEW is that you can write the code and compile it for the target without having to purchase the equipment first. You could program the algorithm, and then understand what size FPGA, you put on.

Bruce

Tags: NI Software

Similar Questions

-

Hello

I am trying to configure a component LabVIEW and xilinx coregen won't let me because «is not installed with labview fpga xilinx ise» I can't find a proper download of NOR. Is this a question expected? There is of course the xilinx website, but do I need a specific version and how can I say? The target FPGA's Virtex-6 LX195T if that's a factor. LabVIEW 2013.

http://sine.NI.com/NIPs/CDs/view/p/lang/en/NID/210629

Hey, ToeCutter,.

You have the 2013 LabVIEW FPGA Module Xilinx tools installed locally? Who has Xilinx coregen, which is what you will need to configure their intellectual property. If you are some intellectual from the LabVIEW FPGA palette, it should "work".

-

Zip file and iso LabVIEW FPGA Xilinx tools 12.4 Module is broken

I downloaded the two zip file of LabVIEW FPGA Module Xilinx tools 12.4 and iso image file three times to make sure that both files are broken and can not be installed!

The size of the file is so large about 3g. It would be better to double-check before you download on the Web site.

-Very well,.

The download is complete and the standard Windows Extraction tool worked, WinRAR worked and 7Zip worked (and no, I don't know why, I installed all). I did download a wireless network that does not have direct access to our internal servers, it should therefore be a test valid. If the link I provided above was not that you used (probably isn't, because it is not an ISO option), could you please provide me with a link to the page that you used so that I can test and repair? In the meantime, the link above should work for you.

-

LabVIEW FPGA Xilinx tool claims his license has expired.

I recorded the two & Labview Labview FPGA on my PC and the PXI chassis.

However, when I try to compile my code, I get this error message:

ERROR: Xst:1531 - for this trial software evaluation period has expired.

According to the agreement of the assessment, which has been shipped to you

as well as the trial CD, this software will be is more exploited.

We look forward to help you as you make your assessment of the Xilinx

solution. Your sales engineer local domain or the seller is available

for any questions or help you in the purchase of an annual plant

software license. You can also contact Xilinx directly at [email protected]

Thank you for the assessment of the solution of Xilinx. Thank you for your interest for

Xilinx and look forward to earning your trust and your business.

ERROR: Xflow - program xst returned error code 1. Aborting the workflow execution...I didn't think I need to buy something more in addition to Labview FPGA. Is this a bug?

-

64-bit driver for LabVIEW FPGA Xilinx SPARTAN 2009 3rd starting Board

My dear I need this add-on

We I install the module i hava, it seems

Support for LabVIEW for Spartan-3E (incompatible with the 64-bit platform)

is their a supprt 64-bit version?Best regards

Hello mangood,.

There is unfortunately no way to use the driver on 64-bit Windows. You will need to use the 32-bit operating system to use the Spartans drivers. Sorry for the inconvenience.

-

Pilot LabVIEW 2010 FPGA Xilinx SPARTAN 3 Board starting

Dear friends,

Is it possible to publish a LabVIEW FPGA Xilinx SPARTAN Driver 2010 3rd starting Board?

Kind regards

WEDO

-

Drivers Xilinx/Multisim and Labview FPGA

Where can I find drivers for my FPGA OR if I use Multisim/Xilinx and NOT of Labview? All the links I found are Labview be installed. However, the explicit manual FPGA indicates that you can use Multisim/XIlinx ISE in place.

OK, I tested just outside. The Driver of LabVIEW 2013 DEFB contains 2 separate components, the driver and Module FPGA support. If you run this installer, it won't check if you have LabVIEW FPGA installed unless you check the box for LabVIEW FPGA support.

I can change the text in the Installation Instructions to read "LabVIEW FPGA 2013 is required to install the LabVIEW FPGA Module Support component installation".

-

Download NI LabVIEW FPGA Module Xilinx Tools 10.1 2013 problems

I'm trying to download the Xilinx tools 10.1 to use with a chassis 9113 in LV2011. Based on this white paper, that the compiler below should work perfectly. The problem is that I can't seem to download all the way.

I can't seem to cross ~ 336MB using the standard or the downloader OR. Any ideas? Does anyone else have this problem?

http://www.NI.com/download/LabVIEW-FPGA-Module-2013/4249/en/

Thank you

-PBD

Well well... on the good side of things, you don't want 10.1 anyway!

Virtex-5 LX50 FPGA<- requires xilinx="">

10.1 is only for devices FPGA Virtex-II! (.. .after LabVIEW 2009 it was, just for all of you who read this know).

so... try this link: http://www.ni.com/download/labview-fpga-module-2013/4248/en/

-

Pilot LabVIEW 8.6 and FPGA Xilinx SPARTAN 3 departure Board

Is the new LabVIEW compatible driver FPGA Xilinx SPARTAN version 8.6 3rd starting Board?

I mean the download found here...

http://digital.NI.com/express.nsf/bycode/Spartan3E?OpenDocument&lang=en&node=seminar_US

Tutu

Spartan-3F for LV FPGA 8.6 support is under development. Contact your engineer commercial ground NOR or Sapper University if you will need a copy of the draft.

Reid

-

Please help me for this problem "error starting compile step: make sure that a compatible version of Xilinx tools is installed in the location specified in the setup of LabVIEW FPGA.»

Look for the error on the Web site of or or on the forums. Take a look at the following links:

http://forums.NI.com/NI/board/message?board.ID=170&message.ID=381394&requireLogin=false

http://forums.NI.com/NI/board/message?board.ID=170&message.ID=205754&requireLogin=false

-

LabVIEW FPGA: Integration node clock wrong

Hello

I'm having some difficulties to understand how the clock is part of the node IP for LabVIEW FPGA and was hoping to get some advice.

What I try to do is to set up a digital logic circuit with a MUX feeding a parallel 8-bit shift register. I created the schema for this Xilinx ISE 12.4, put in place and can't seem to import the HDL code into an intellectual property node. When I run the VI, I am able to choose between the two entries for the MUX, load the output in the shift register, clearly the shift register and activate the CE.

My problem is that when I switch to the entrance of THIS, he should start 1 sec shift (Boolean true, SCR, High, what-have-you) in the registry once each clock period. Unfortunately, it instantly makes all 8 bits 1 s. I suspect it's a question of clock and here are some of the things I've tried:

-Specify the input clock while going through the process of configuring IP nodes.

-Adding an FPGA clock Constant as the timed loop.

-Remove the timed loop and just specifying the clock input (I'm not able to run the VI that I get an error that calls for a timed loop)

-Do not specify the clock to enter the Configuration of the IP node and wiring of the FPGA clock Constant to the clock input (I can't because the entry is generated as a Boolean).

-Remove an earlier version of the EC who had two entries up to a door and at ISE.

-Specify the CE in the process Configuration of the IP nodes.

-Not specify this in the process of setting up nodes IP and wiring it sperately.

-Various reconfigurations of the same thing that I don't remember.

I think I'm doing something wrong with the clock, and that's the problem I have. Previously, when I asked questions to the Board of Directors on the importation of ISE code in LabVIEW FPGA, a clock signal is not necessary and they advised me to just use a timed loop. Now, I need to use it but am unable to find an explanation online, as it is a node of intellectual property.

Any advice would be greatly appreciated, I'm working on a project that will require an understanding how to operate clocks the crux of intellectual property.

Thanks in advance,

Yusif Nurizade

P.S. I have attached my schematic ISE and the LabVIEW project with one of the incarnations of the VI. The site allow me to add as an attachment .vhd file, but if it would help I could just paste the body of the code VDHL so just let me know.

Hello Françoise,.

I spoke to the engineer OR this topic and it seems that it was sufficient to verify that your code works, by putting a wait function of 500 ms on the while loop to check that the registers responsible and clear. I'm glad that it worked very well!

-

How to import codes Verilog in LabVIEW FPGA?

I tried to import the Verilog code by instantiating followed education in http://digital.ni.com/public.nsf/allkb/7269557B205B1E1A86257640000910D3.

but I can still see some errors when compiling the file VI.

Test file simple Verilog is as follows:

==============================

module andtwobits (xx, yy and zz);

input xx, yy;

output reg zz;always start @(xx,yy)

ZZ<= xx="" &="">

end

endmodule==============================

and after you follow the above link, we have created the instantiation as file

==============================================

Library ieee;

use ieee.std_logic_1164.all;mainVHDL of the entity is

port)

xxin: in std_logic_vector;

yyin: in std_logic_vector;

zzout: out std_logic_vector

);

end mainVHDL;architecture mainVHDL1 of mainVHDL is

COMPONENT andtwobits PORT)

ZZ: out std_logic_vector;

XX: in std_logic_vector;

YY: in std_logic_vector);

END COMPONENT;Start

ALU: andtwobits port map)

ZZ-online zzout,

XX-online xxin,

YY-online yyin);end mainVHDL1;

==============================================

Sometimes, we observe the following error when we put the flag on the output port.

ERROR: ConstraintSystem:58 - constraint

TNM_ChinchIrq_IpIrq_ms; > [Puma20Top.ucf (890)]: INST

"* ChinchLvFpgaIrq * bIpIrq_ms *" does not correspond to design objects.

ERROR: ConstraintSystem:58 - constraint

TNM_ChinchIrq_IpIrq; > [Puma20Top.ucf (891)]: INST ' * ChinchLvFpgaIrq * bIpIrq. "

does not match design objects.and Interestingly, if we remove the indicator from the port of exit, he sucessfully compile on the LabVIEW FPGA.

Could you take a look at and please help me import Verilog to LabVIEW FPGA?

I followed the basic steps of the instantiation on the link above, but still it will not work.

Please find the attachment for all files.

-andtwobits.v: original file from Verilog

-andtwobits.ngc: file UCS

-andtwobits.vhd: VHD file after translating a simulation model

-mainVHDL.vhd: master of the instantiation

Since there is no sample file for Verilog (VHDL file, there but not for Verilog), it's a little difficult to do simple execution on LabVIEW FPGA, even for examples.

Thank you very much for your support, and I'm looking forward to seeing all your help/answer as soon as possible.

Records,

The best instructions we have for integration Verilog IP in LabVIEW FPGA can be found here: using the Verilog Modules in a component-level design. My suspicion is that you did not uncheck the option 'add the IO buffers' in the Xilinx ISE-specific Options parameter when running XST (see page 8 of the .pdf)

-

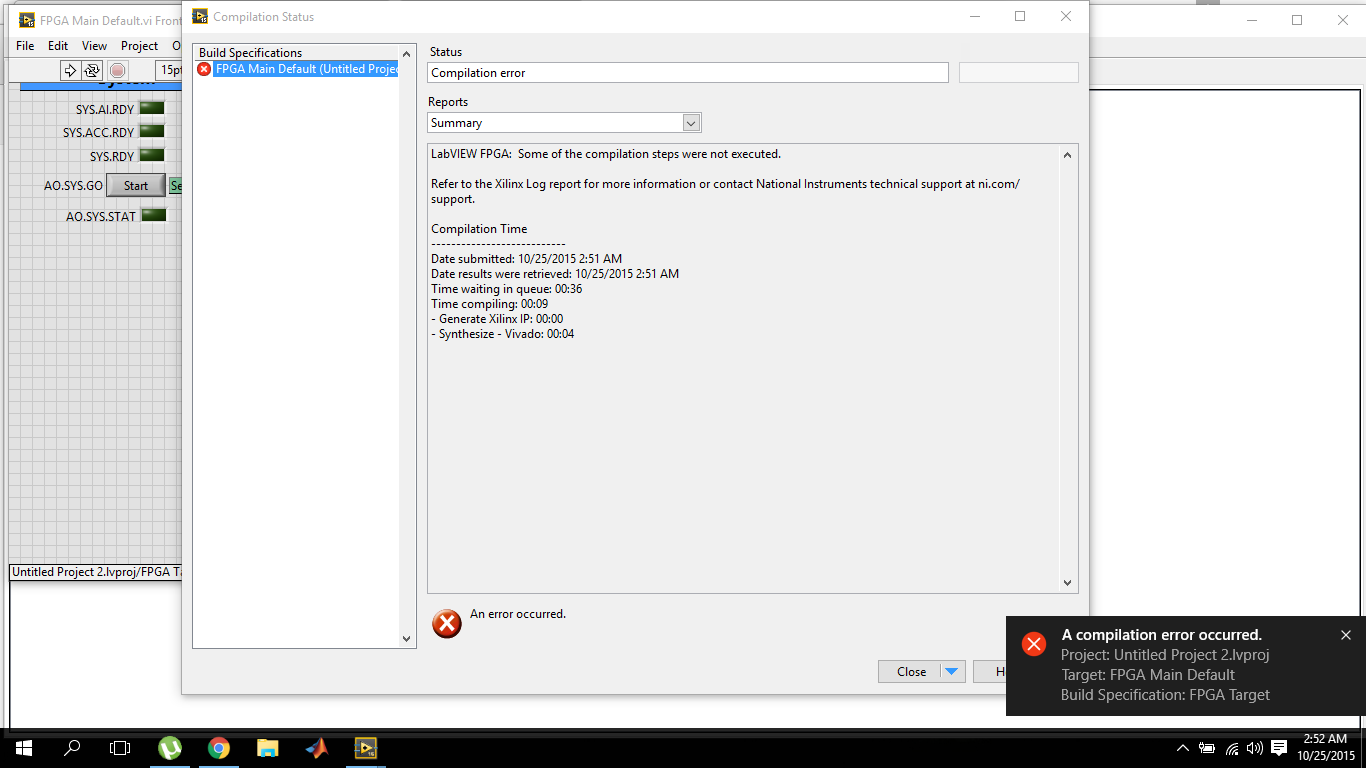

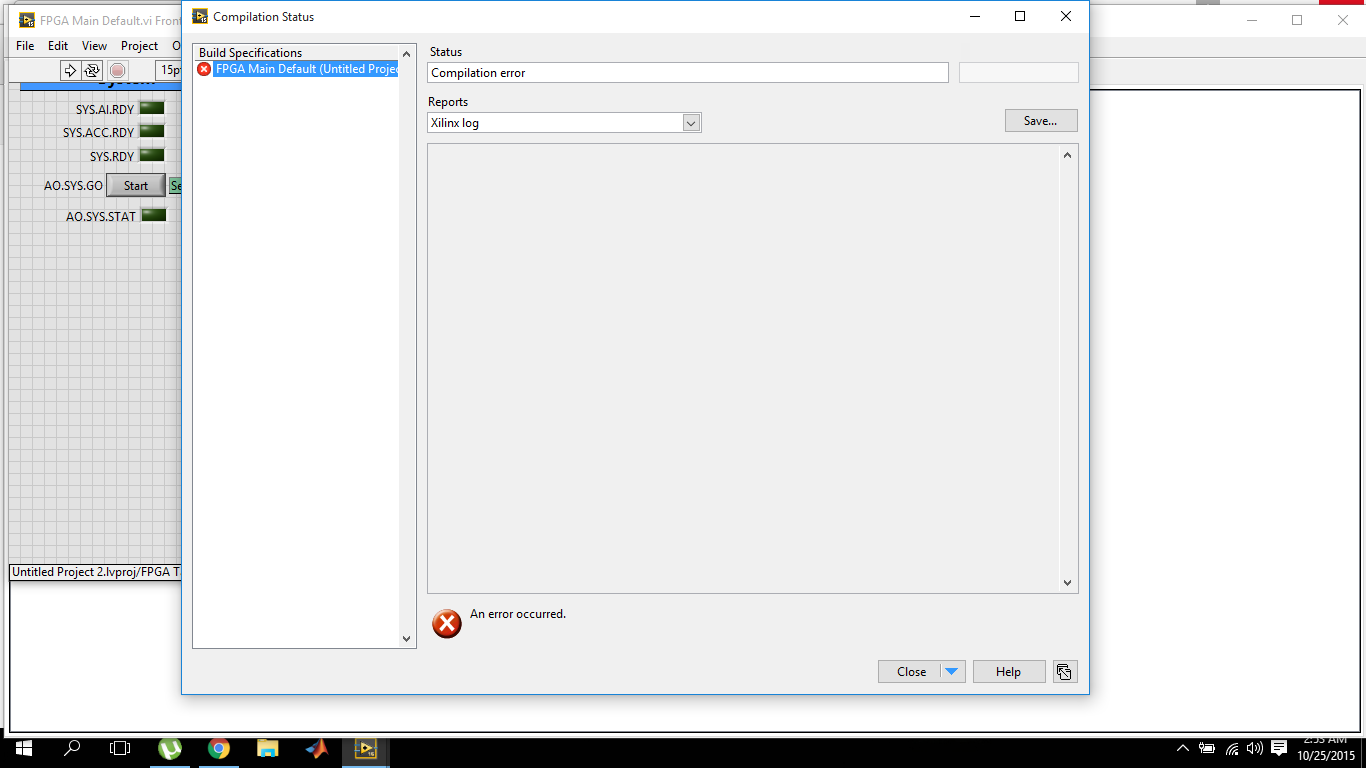

LabVIEW FPGA, 2015 compilation error

I've recently switched to LabVIEW 2015 and I'm working on OR myRIO. So also installed myRIO 2015 bundled software. The problem I have is that the compilation of fpga fails within 10 seconds.

and the target Xilinx journal report is empty

The first time when I tried to compile on 2015 version, it failed and the message box that failed came alongwith the avast antivirus warning for malicious activity. I reported it as wrong and now I tried several times with avast shield disabled control, but the results are the same. While the version of labVIEW 2014 works very well.

Now, I'm sure that there is something wrong with the installation of Vivado because this dll is part of it. The dll must be default in the2014_4\lib\win32.o directory C:\NIFPGA\programs\Vivado if you are using an operating system for 32-bit AND also in C:\NIFPGA\programs\Vivado2014_4\lib\win64.o If you use a 64-bit operating system. If the dll is not here, it is probably that the anti virus (I've never seen what happens to Xilinx but I have for other stuff).

I'm emphasizing the 2014_4 because LabVIEW 2015 uses Vivado 2014_4 while 2014 LabVIEW uses Vivado 2013_4. Since you have also installed LabVIEW 2014, you must have 2013_4 as well and if it works, you will find the dll I just wanted you make sure you check the correct directory for the Vivado 2014_4.

Download and install (reinstall or repair if already installed) 2015 LabVIEW FPGA Module Xilinx tools Vivado 2014.4. You can also use the DVD Setup if you have. It would be a good idea to do the installation with the disabled and even anti-virus try the first compilation the same. Try and let me know if the problem persists.

Kind regards

-

Move from LabVIEW FPGA block of ram address to node CLIP?

Hello

I need to pass an index memory RAM of LabVIEW FPGA block to a CLIP node to the node CLIP to have access to the data in the BRAM. The node of the ELEMENT contains an IP address that we developed and the IP address is the use of Xilinx BRAM driver to access data. I guess that we need to move the physical address of the BRAM to the ELEMENT node.

Is this possible? If so, how? If this is not the case, what would be an alternative?

Thank you

Michel

If I understand you correctly, Yes, you should be able to use the memory block of the Xilinx pallet Builder in LabVIEW FPGA and in the loop of the single Cycle, connect the ports of this block signals CLIP exposed by the IP of your colleague. You may need to tweak/adapt some of the signals slightly to the LabVIEW data flow.

-

When I compile a labview fpga VI, (my version of labview fpga is 2014), I get the not found error Xilinx 10.1 build tools.

But for 2014 labview, version 14.7 Xilinx is the only compatible and that I installed. But it is still asking for Xilinx version 10.1. I tried both with configured CompactRIO and also a vi without hardware. The same is repeated each time.

What can be the problem? Please help me.

Elodie

What FPGA target do you use? I think for Virtex 2 target Xilinx 10.1 tools are used.

Maybe you are looking for

-

By connecting to facebook lately (in the usual help of the login page for the Canada facebook or facebook.com), opens the usual page, but then a dialog box appears stating "you must be logged" which also provides form for email and password boxes. It

-

Satellite A50-111: I get an error: cannot install MBR disks

I have a satellite A50-111. The system with the error would not start a system disk and tried to boot from the network. To get the pc working, I tried to reinstall Win XP Pro, but I get an error: cannot install MBR disks How to solve this? Jon

-

Windows Live Mail Fail-ID: 0x8DE00001

Is something wrong with the server 4102 Det gar inte att skicka eller your emot meddelanden for kontot Hotmail (jan.hylen). Serverfel: 4102Server: 'http://mail.services.live.com/DeltaSync_v2.0.0/Sync.aspx '.Windows Live Mail Fel - ID: 0x8DE00001

-

HP Envy 5643: HP Envy 5643 "is" not my SSID

Bought a new printer that I had this same problem with my old HP Deskjet 3510. But try to set this one up too, I'm having the same problem. Performing the installation, when the SSID is pulled upward, everyone around my neighborhood pulls up, except

-

WAP11 - no assinged network using WEP address

My 2.6 WAP11 connection (Internet) very well if WEP is not defined. If WEP is defined, then I always get "limited or no connectivity" because "the network has not assigned a network address" even if a connection to the WAP11 is made. I use the WAP11