Accurate cycle of FPGA simulation error

Hello.

I have problems simulating an FPGA vi with a third party Simulator.

I took the example of the tutorial found at http://zone.ni.com/devzone/cda/tut/p/id/12942 , but I get the error of dialogue (see attachment) during the construction of the export of the simulation.

I put in the LabVIEW options the Simulator to ISim.

The text in the details section of the dialog error box is:

Error-61499 occurred at niFpgaSimulate_GenerateCompileOrder.vi<><><>

Possible reasons:

LabVIEW FPGA: An internal software error in the LabVIEW FPGA Module has occurred. Please contact National Instruments technical support on ni.com/support.

There was an error in the compile command generation. The file that caused the problem is... / niFpga /... / niFpga/PkgNiFpgaSimulationModel.vhd. For more information, see compileOrder.log in the directory of niFpga simulation. The error information is less to:

Line 53: Syntax error near ', '.

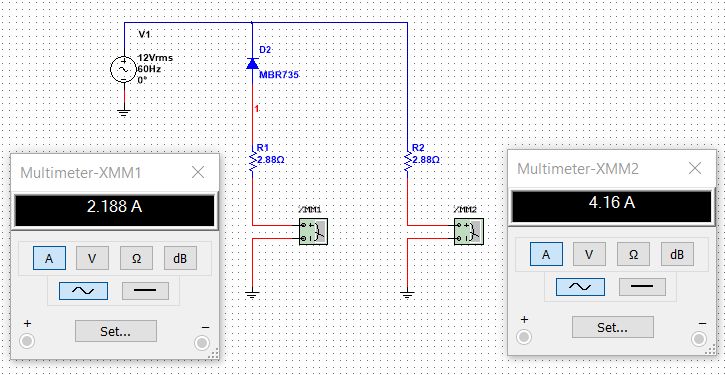

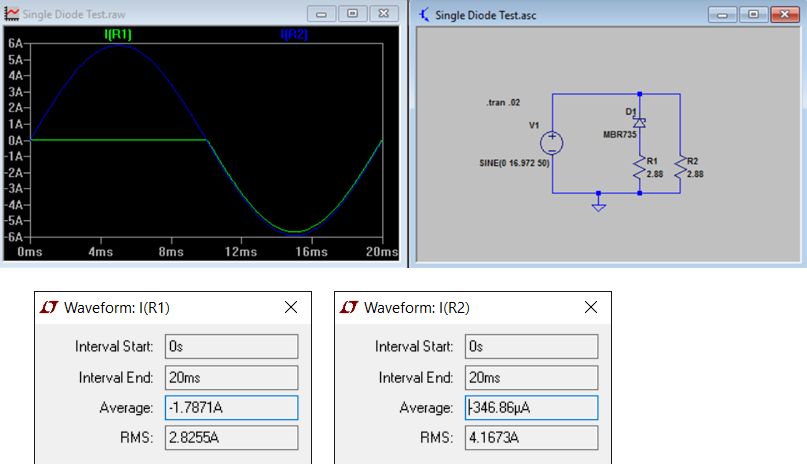

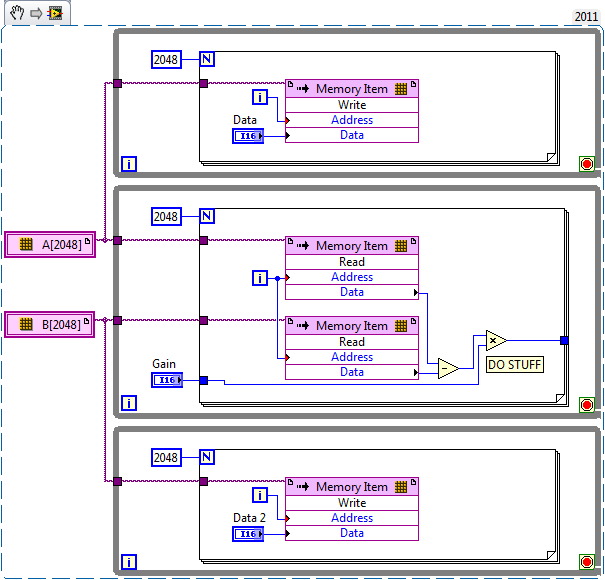

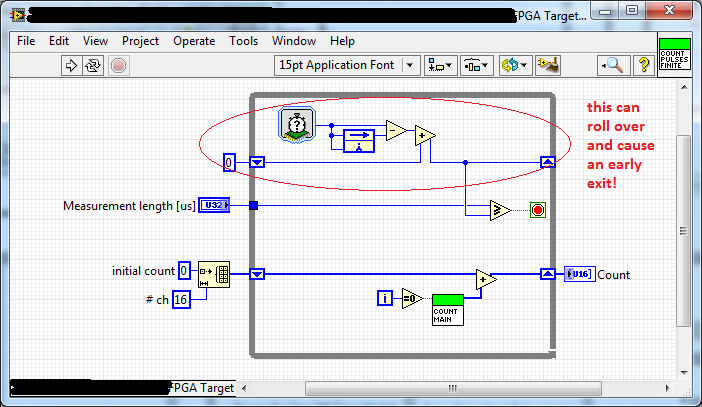

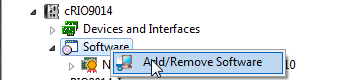

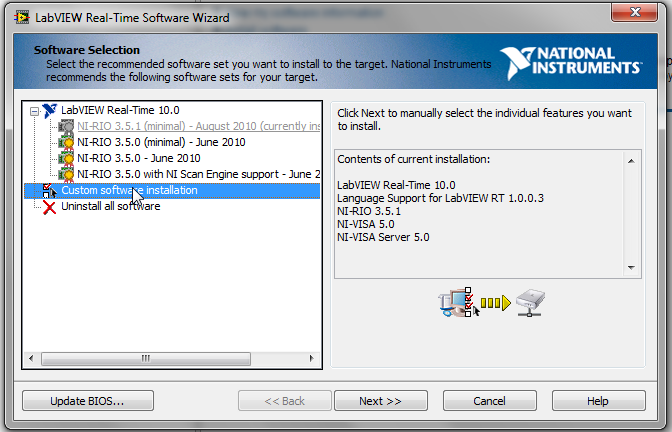

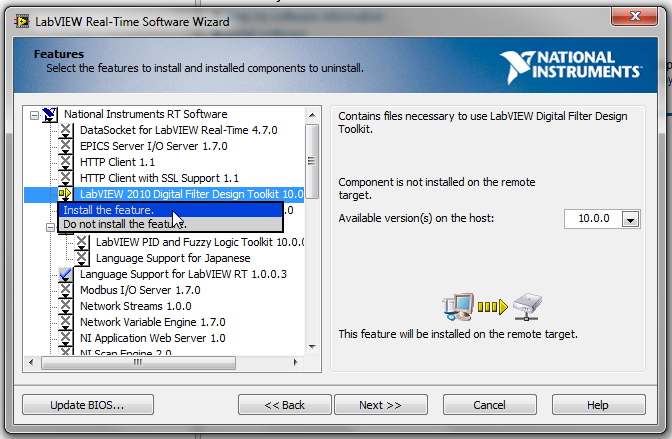

Using LabVIEW 2011 (Xilinx tools 12.4) on Windows 7 Pro 64 bit. Any help would be appreciated. Thank you. Hello It seems that there is an article in the knowledge base that describes the error you see. Let me know if it solves your problem. See you soon,. Ryan Tags: NI Software I am trying to simulate Hi Anastvl, Your mapping of the model was not properly Setup. The next section of the model is very important, he says the model and order pins, you need this information to properly table parameter mapping in Multisim. The first pin reported in this model is not inverseuse entry, second pin said entry.. inversion last pin was released. The key is to watch the line model subckt and to know the order that the pins are reported. * / / / MAX414 MACRO. In Multisim, the mapping of the model below table. Under the column 'Model nodes' are when you map the order of pin code subckt of the model line. You should consult the tutorial below for a guide to component to create a component of several section. Open vi FPGA gives error xnode (Lv 8.6) (not executable) Hello I wrote my description of the error also here: http://forums.ni.com/ni/board/message?board.id=280&message.id=5055&jump=true#M5055 When using "run vi on the development computer" I get an error broken pointing me to the "open FPGA vi function", the problem be 'an xnode object is not executable. I have not found this problem under discussion anywhere, I tried uninstalling FPGA and Rio soft. and resinstalling, but not help. All ideas are welcome. Thank you Staffan Hello JMota wrote: "Here's something to try. I think that the configuration of your FPGA target to run on the development computer (with simulation of IO) will not work if you try to run your host VI on RT. test by dragging the VI to my computer and run it from there. Altenatively, you can reconfigure your FPGA target for not performing on the development computer (what used to be called emulation). Hope that explains why the VI has broken. » And it solved the problem - works fine now - if this issue is resolved. Staffan Hi all Please, for the love of God can someone take a look at the attached FPGA project, I hit to the top and tell my why it is that whenever I run, as soon as he's trying to read/write on the host computer, it returns error-61046? A screenshot of the error is included in the attached .zip file. I made many programs FPGA before with no problems, while using the same FPGA and FlexRIO module and never had this problem. If I run an example program it works fine so I am confident, that the error lies in my programming, I can just see where! As you can see all the clocks are internal and appear to be configured correctly according to the example programs and other programs FPGA, that I have done before, so I'm puzzled. I hope that it is just my stupidity and lack of coffee. Congratulations in advance. Mitch The pilot FlexRIO comes two CLIPs for the 5781. At ' a "NI 5781 Sychronous system" OR 5781 "VIDEO CLIP. The "NEITHER 5781' is what originally delivered with the FAM and is always delivered with the driver for legacy purposes. I would discourage the use of this CLIP because it uses regional clocks for IO Module clock 0/1 which limit the amount of fabric that can be driven by these clocks to the fabric available in the respective region of the FPGA. The advantage of this CLIP, it's that the ADC and DAC can be clocked at different rates through a clock divider that exposes the CLIP. The 'NI 5781 Sychronous system"CLIP is what is recommended for all new models. It uses a world clock which can target tissue in all regions of the FPGA. This CLIP uses the same clock to drive the ADC and DAC (IO Module clock 0). IO Module clock 1 is not used in this CLIP. If you used the sychronous CLIP system and always a logic had driven out by IO Module clock 1 it that would explain why you received the error of non-response from IO Module clock 1 is left connected in the sychornous CLIP system. I had problems with a more complex circuit that I played with, and I've narrowed the problem down to handling of Multisim diodes during the simulation. The circuit below shows two branches that have identical resistances but there is a diode in series with it if she performs only other each half cycle. It is a rectifier and theory tells us to wait for the RMS current through resistance to 70.7% of the current flowing through a resistance that does not have the diode in series (for an ideal diode). For R2 below I (R2) = 12/2.88 = 4 .16A and this is properly determined by XMM2 multimeter. The current in the branch of the diode must be 4.16 * 0.707 = 2.94 A but as you can see XMM1 multimeter is far away. I changed the led a virtual model and the current has dropped to 2.14 A... I checked this with the same values of resistance and the diode model using LTSpice and I get the correct results with this program (which allows Fior diode charactersists)... I have attached two files (Multisim 14 and LTSpice) simulaiton for reference. So what is happening here? Hi Myamigo Thanks for that information, I think that the issue here is with the multimeter and not with the circuit. I used a current probe and got A 2.8 on this line. I enclose a picture showing this. I think that this may be due to a configuration on this unit or it can also be a CAR, but I need to conduct additional research on this to see if it is a wrongful conduct of Multisim multimeter. tables of fixed size in FPGA compilation error - how to implement a waveform control in an FPGA? Hello After being stuck for two days, please let me briefly describe my project and the problem: I want to use the cRIO FPGA for iterative control of waveforms. I want to capture a full period of the waveform, subtracting a reference waveform period and apply control algorithms on this. Subsequently the new period of correction must be sent again for the output module OR. If it does not work, the captured waveform will look like the one reference after several iterations. I am planing to create an array of size fixed for the capture and the reference waveform (each around 2,000 items for a given period). I use so 2 paintings of each elements of 2000. I use the function 'replace the subset of table' to update each element captured in the loop sampling and a feedback for each table node to keep in memory (I also tried shift registers, but then the berries do not have a fixed size any more and I can't start the compilation process). If I try to compile the FPGA vi, I get the following error: Details: Before I added berries to my code I could compile the FPGA without problems. So, it seems that the tables are too big for the FPGA. :-( Therefore, I would like to ask if there is perhaps a better method to implement my problem in LabVIEW FPGA? How could avoid the tables to save my waveforms on a period? Thanks a lot for your help in advance. Best regards Andreas Unfortunately, the LabVIEW FPGA compiler cannot deduct stores shipped from berries (yet). When you create these two large paintings, you are creating essentially several registers very, very large. Just by looking at your picture, I guess that there are at least 4 copies of each of the tables. You want to use LabVIEW FPGA memories instead. You can create memories outside the loop and then read/write them where you are currently referencing the berries. The only change that you really need to do is to break down your treatment in scalar operations. I have attached a simplified version of your plan, I hope it helps. Let us know if you have any other questions. Compilation of FPGA 61330 error on a cRIO Hi all Currently, I have to rebuild a fpga bitfile to reflect a new hardware configuration on a cRIO. I have installed on my computer, tools that have been able to compile the bitfile several times; but now I get an error when I compile. I have attached two images of the error to this message. I'm currently under this software configuration: It turns out it was a firewall issue. I had turned off my firewall, but there was a tertiary process still running. I added a few my firewall exceptions, which should allow the program to work, but it didn't. Once I deleted these exceptions, the compiler run with no errors. I think it's time to get a new firewall program. Thanks for all your help. I'm converting a piece of code from 8.5 to 2011. When I tried to compile the fpga vi to a bit file, I get the error attached. Why is this? Thank you! The thing is that the only solution that I found about this error is to install a patch or repair/reinstall Xilinx or LabVIEW FPGA tools. Christian FPGA compilation error sbRIO 9632 Hi guys,. I'm trying to write a simple piece of code to send a PWM signal to a PIN on my sbRIO-9632 (starter kit 2.0) to order a servo. I used the example of 'control a servo using PWM' and my code is pretty much the same. When I try to generate/compile the FPGA VI, it stops after only 4 to 6 minutes, saying an error has occurred. The compilation appears to hang during the process of the "card". The example is for a sbRIO-9631 so I created a new project for my robot Robotics and changed the PIN e/s that I use (Port5/DIO9). I search through forums but cannot find a solution to this :/ I have attached my code and the XilinxLog file with it. Thanks for any help! MortZ Hello Sorry for the late reply! Have you made progress? Unfortunately, your zip file seems to be disabled on my PC. How it has been compressed? So what I meant by remove the digital Pulse.vi to generate, is to see if it affected the compilation. Please see if you can compile the FPGA code with the following approach: Create the new project > add your target sbRIO > add the VI attached to this post to your FPGA target > compile I think it would be beneficial to you to see if the problem is the compilation itself or the code you are trying to compile. In addition, you have any another available PC? Might be a good idea to see if your code compiles on another PC. Please make sure you have LabVIEW Real-time and LabVIEW FPGA installed (it should come with the Robotics module, but I recommend that you check that they have indeed been included). If the build process fails to map no matter what you do, I propose the following: make sure that the target passes a self-test of MAX. reinstall the Xilinx tools (only if it seems that the issue is not with the code, but with the compilation process itself). Good luck Best regards Christopher How to manage the turnover in number of cycles of FPGA output? I wrote a little VI that counts ticks on a set of lines of DI for a period of time. It uses the number of cycles of VI to determine how much time has passed since he started running. The output of this VI is a U32, and subtraction function looks like it going to saturate to '0' if the number of cycles longer rolls. How can I handle this situation to prevent the VI to leave earlier? Integer arithmetic must manage calculation rolling correctly (for example if your value is a U8 and you do 3-250, you should get 9). I guess (although I never checked) it works even in the FPGA. You can do a simple check yourself with explicit code. It would be nothing less than a complete cycle of safe, so it depends how much time it takes. If it is ms, it would take about 50 days. In your case, it seems that you have configured the service to be in us, so it would be somewhere more than an hour. If that's not enough, then you can maintain the real value in a U64 and then take the number of us that passing in each iteration and that adds to the U64. LabVIEW RT/FPGA Compling error with NI_DigFilterLicensed.lvlib Hello I'm trying to compile a program for my sbRIO-9632, but I got following error: Deployment NI_DigFilterLicensed.lvlib:dfd_Filter Signal by Signal of Coef.viNI_DigFilterLicensed.lvlib:dfd_Filter of Coef.vi loaded with errors on the target and was closed. This filter is not compatibel to Labview RT? I use RT 2009SP1, SP1 FPGA, Labview, SP1 and 3.4 OR RIO. Thank you very much Attached to the status of full deployment: Deployment NI_DigFilter_Design.lvlib:dfd_Group Delay_Gradient Optimization.vi (15.72 K) Hello chefweb, Make sure you have installed Toolkit Digital Filter Design and it is operated properly, then follow the screenshots below in your measurement & Automation Explorer (MAX): DMA FIFO of FPGA compilation error Hello I have a cRIO 9074 with FPGA. I tried a simple piece of code to learn how to acquire the data that is generated on the FPGA at a rate of 10 KHz and transfer it to the host VI to treat later in offline mode. However, I meet this compilation error when you compile the FPGA VI base containing a node to write FIFO (photo of the VI attached below). In compiling the report, it is said that there are 256 RAM Block used (the total number is 40), so an error has occurred. The error notification of exact compilation from Xilinx report is reproduced below: # From the PAM program # o toplevel_gen_map.ncd - intstyle xflow-calendar toplevel_gen.ngd map toplevel_gen. FCP #----------------------------------------------# "Target part using" 3s2000fg456-4 ". Design of mapping in the lut... Guided running of packaging... Running based on the delay of packaging of LUT... ERROR ERROR: card: 115 - the design is too large to fit the device. Please consult the Design summary section to see what resource requirements for your design exceeds the resources available in the device. Note that the number of slices don't notice it that their packaging could not be completed accurately. NOTE: A file NCD will be always generated to allow you to examine the mapped design. This file is intended for evaluation use only and will not be processed successfully by means of BY. Mapping performed. See the report of map file "toplevel_gen_map.mrp" for more details. Problem encountered during the packaging phase. Summary of design -------------- Error number: 2 Number of warnings: 125 ERROR: Xflow - card program returned the error 2 code. Aborting the workflow execution... Bitstream not created Time history analysis What does that mean? How can I fix this error? Thank you Bogdan Hey,. Have you already tried to reduce the size of the FIFO memory? Christian cRIO 9014, FPGA compiler error I use cRIO 9014, that while the FPGA code compilation I get attached error. Please guide me ob who... Hi Olivier,. The displayed error is clear. Your system time is older than the time of installation. Change to correct time and try it... In addition, if you change your system time (IE computer), some software will not work. (another example is Gmail. Try to connect to Gmail after year settting in the previous year in your system. It displays error SSL.). Microsoft Train Simulator error Setup error "Unable to verify the media" keeps coming back. Original title: Microsoft Train Simulator Setup error Try to install Microsoft Train Simulator on vista and when installing on the error 'Failed to check media' 2nd drive keeps coming back. Have also tried on another computer that has XP and the same results. Can anyone help? Hi Rick, Given that the CD does not work in Windows XP computer also, there seems to be a problem with the drive itself. Clean the CD or the DVD. To do this, use a disc cleaning kit. Or gently wipe the silver part of the disc with a soft and Lint cotton cloth. You can read the following article and check. If you are always faced with the question, so you may need to replace the drive. JDE Simulator error "reload software: 552". Hi, I use Blackberry JDE version 4.7 with Simulator 4.6.0.150 bold 9000. Everything works fine an hour ago. It just started to show "reload software: 552" all of a sudden. He have no importance how to start the simulater, JDE debuger, or simply run the Simulator booth along. There is a solution to a real device for this error message, but what it means for a Simulator? Thanks for your help. Chimera If you run your 4.7 on a "BOLD" device software, you run the risk of "bricking" of the device, then do not. The JDE 4.7 has only a simulator of the storm, because the storm is the only device which manages 4.7 OS. If you want to target the "BOLD", then use the 4.6 JDE or more LOW (no more). I created a partition (accidentally) and now I can't load Bootcamp at startup. Here's the story. I tried to enlarge my Bootcamp partition, but I accidentally did was to create a THIRD partition of its own. I deleted this partition later, but now when I start the computer and hold down the "Alt/Option" I get two options: my Mac Access point Cisco does not recognize correctly entered the WPA pre-shared key My router is a Cisco DPC/EPC2325 DOCSIS residential gateway with wireless access Point. When connecing to Internet via a wireless adapter, this device does not accept the good WPA pre-shared key. I have no similar problem with another PC. Please noti checking windows process in Task Manager How can I check the process in the Task Manager to see what they really are, and if they are a problemor maybe a problem of Annozero? Cannot update Windows Media Player security update I tried to download a book from library using Overdrive and it wouldn't work. He said that I needed to update the Media Security Update window. I did and I said OK to download the file, it gave me a message saying "a security upgrade is required to WRT 1200AC speed Test does not Test of speed inside the router no longer works. Slow to respond and speeds from offshore. I was wondering? My version of flash player is 19.0.0.245. My router's firmware version is 1.0.4.167471. V.2.2.0 speed in the router test. Speed test b

ERROR: HDLCompiler:854 - "... / niFpga /... / niFpga/PkgNiFpgaSimulationModel.vhd" line 13:

ERROR: HDLCompiler:688 - "... / niFpga /... / niFpga/PkgNiFpgaSimulationModel.vhd" line 65: pkgnifpgasimulationmodel statement Package is not yet compiled

ERROR: HDLCompiler:69 - "... / niFpga /... / niFpga/PkgNiFpgaSimulationModel.vhd" line 73:

ERROR: HDLCompiler:69 - "... / niFpga /... / niFpga/PkgNiFpgaSimulationModel.vhd" line 79:

ERROR: HDLCompiler:69 - "... / niFpga /... / niFpga/PkgNiFpgaSimulationModel.vhd" line 81:

ERROR: HDLCompiler:69 - "... / niFpga /... / niFpga/PkgNiFpgaSimulationModel.vhd" line 77:

ERROR: HDLCompiler:69 - "... / niFpga /... / niFpga/PkgNiFpgaSimulationModel.vhd" line 89:

ERROR: HDLCompiler:69 - "... / niFpga /... / niFpga/PkgNiFpgaSimulationModel.vhd" line 90:

ERROR: HDLCompiler:69 - "... / niFpga /... / niFpga/PkgNiFpgaSimulationModel.vhd" line 95:

ERROR: HDLCompiler:617 - "... / niFpga /... / niFpga/PkgNiFpgaSimulationModel.vhd" line 95: nearby; prefix must designate a scalar or array type

ERROR: HDLCompiler:69 - "... / niFpga /... / niFpga/PkgNiFpgaSimulationModel.vhd" line 98:

ERROR: HDLCompiler:69 - "... / niFpga /... / niFpga/PkgNiFpgaSimulationModel.vhd" line 100:

ERROR: HDLCompiler:69 - "... / niFpga /... / niFpga/PkgNiFpgaSimulationModel.vhd" line 102:

ERROR: HDLCompiler:69 - "... / niFpga /... / niFpga/PkgNiFpgaSimulationModel.vhd" line 104:

ERROR: HDLCompiler:69 - "... / niFpga /... / niFpga/PkgNiFpgaSimulationModel.vhd" line 97:

ERROR: HDLCompiler:69 - "... / niFpga /... / niFpga/PkgNiFpgaSimulationModel.vhd" line 107:

ERROR: HDLCompiler:69 - "... / niFpga /... / niFpga/PkgNiFpgaSimulationModel.vhd" line 110:

ERROR: HDLCompiler:69 - "... / niFpga /... / niFpga/PkgNiFpgaSimulationModel.vhd" line 113: Error-61499 took place at niFpgaSimulate_GenerateCompileOrder.vi

Similar Questions

Simulation error message: doAnalyses: affect iteration limit

Simulation error message: ac simulation (s) cancelled

Simulation error message: doAnalyses: too small Timestep

Simulation error message: tran simulation (s) cancelled

*

* connections: input no reverse

* | reversal of entry

* | | positive power

* | | | negative supply

* | | | | output

* | | | | |

* NŒUD CONNECTIONS: 1 2 99 50 97

*

. SUBCKT MAX414 1 2 99 50 97

ERROR ortability:3 - Xilinx this application runs out of memory or met a memory conflict. Use of current memory is 4167696 KB. You can try to increase physical or virtual memory of your system. If you are using a Win32 system, you can increase your application from 2 GB to 3 GB memory using the 3 G switch in your boot.ini file. For more information, please visit Xilinx answer Record #14932. For technical support on this issue, you can open a WebCase with this project attached to http://www.xilinx.com/support.

ortability:3 - Xilinx this application runs out of memory or met a memory conflict. Use of current memory is 4167696 KB. You can try to increase physical or virtual memory of your system. If you are using a Win32 system, you can increase your application from 2 GB to 3 GB memory using the 3 G switch in your boot.ini file. For more information, please visit Xilinx answer Record #14932. For technical support on this issue, you can open a WebCase with this project attached to http://www.xilinx.com/support.

"Synthesize - XST" process failed

LabVIEW: Unable to load the shared library LVDFD. *: NormFltH:C on the device target RT.

Deployment NI_DigFilter_Design.lvlib:dfd_Group Delay_Integer Tau.vi (12,93 K)

Deployment NI_DigFilterLicensed.lvlib:dfd_Specific TF Validation.vi (22,94 K)

Deployment NI_DigFilterLicensed.lvlib:dfd_IIR filter Cluster Validation.vi (9,62 K)

Deployment NI_DigFilterLicensed.lvlib:dfd_Create filter Coef of ZPK without Attributes.vi (18.67 K)

Deployment NI_DigFilterLicensed.lvlib:dfd_Get a Quantizer.vi FXP (12,50 K)

Deployment NI_DigFilter_FXP.lvlib:dfd_Validate Quantizer.vi (9,34 K)

Deployment of managers NI_DigFilterLicensed.lvlib:dfd_Error .vi (multiple) (6.89 K)

Deployment NI_DigFilter_Design.lvlib:dfd_Group Delay_Params Validation.vi (22,54 K)

Deployment NI_DigFilter_Design.lvlib:dfd_Group Delay_Initial Guess.vi (12.65 K)

Deployment NI_DigFilterLicensed.lvlib:dfd_TF Validation.vi (13.52 K)

Deployment NI_DigFilterLicensed.lvlib:dfd_TF to filter the Coef.vi (37.91 K)

Deployment NI_DigFilterLicensed.lvlib:dfd_Get Filter Type Coef (filter IO) .vi (13.76 K)

Deployment NI_DigFilterLicensed.lvlib:dfd_Write filter Coefficients.vi (13,97 K)

Deployment floating NI_DigFilterLicensed.lvlib:dfd_Build filter Coef.vi (16.68 K)

Deployment NI_DigFilterLicensed.lvlib FD Build filter transfer Function.vi (13.02 K)

FD Build filter transfer Function.vi (13.02 K)

Deployment NI_DigFilter_Design.lvlib:dfd_Group delay Build Allpass Filter.vi (11,19 K)

Deployment NI_DigFilterLicensed.lvlib:dfd_Set a Quantizer.vi FXP (12,69 K)

Deployment NI_DigFilterLicensed.lvlib:dfd_Read filter Coefficients.vi (14.07 K)

Deployment NI_DigFilterLicensed.lvlib:dfd_Filter Signal by Signal of Coef.viNI_DigFilterLicensed.lvlib:dfd_Filter of Coef.vi loaded with errors on the target and was closed.

LabVIEW: Unable to load the shared library LVDFD. *: NormFltH:C on the device target RT. ack:2310 - type compositions "RAMB16" too found to adapt to this device.

ack:2310 - type compositions "RAMB16" too found to adapt to this device.Maybe you are looking for