compilation process 'Map' FPGA failure failed

Hi all

We bought a new cRIO 9068 and I try to get installed it in a new project with some new maps. We have also improved our projects to LV2013 - sp1. I was unable to complete a compilation of the bitfile FPGA. It takes place during 25 minutes and when it will do the "Utilization, (map) of final device" it fails. Looks like I might be missing something, I have, but I have installed and reinstalled LV2013 and versions of Xilinx (10.1 and 13.4 or 14.4) which does not seem to solve the problem.

Any ideas on what he seeks can be as useful as a search on 'Map' did not help.

Thanks in advance.

I found the solution. There are additional items on the WAY lead the FPGA Compiler for the installation of VS I have instead of the executable 'Map' that she needed. I removed the path to the VC\include directory and now it compiles. Probably screwed my VS, but that's another day.

Tags: NI Software

Similar Questions

-

Failure of compilation of the FPGA target

Hi all

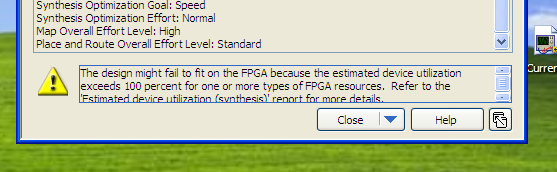

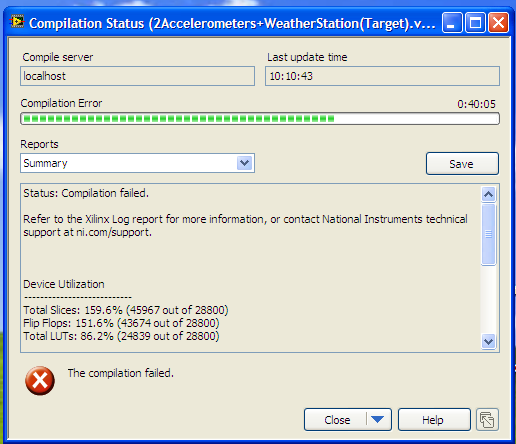

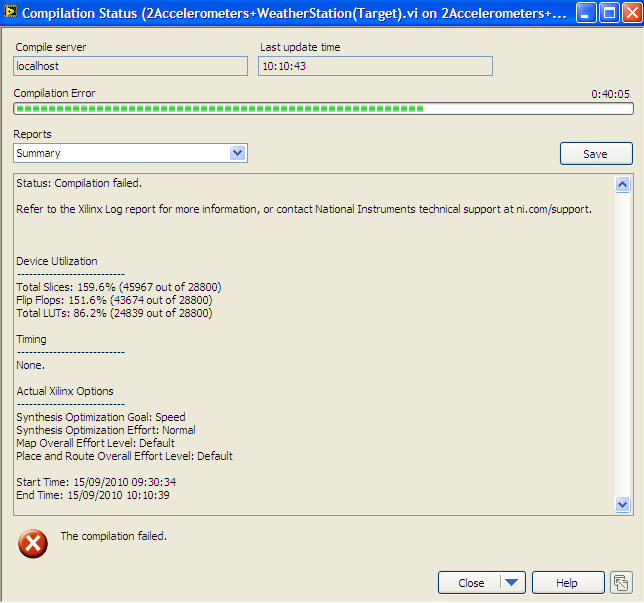

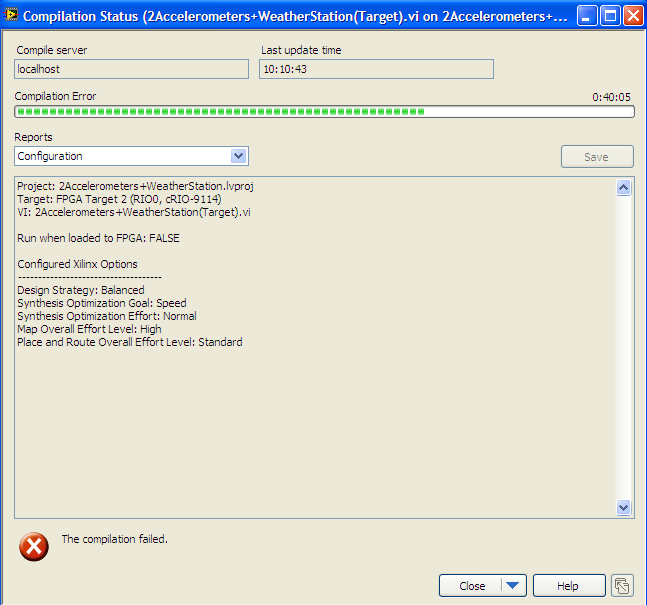

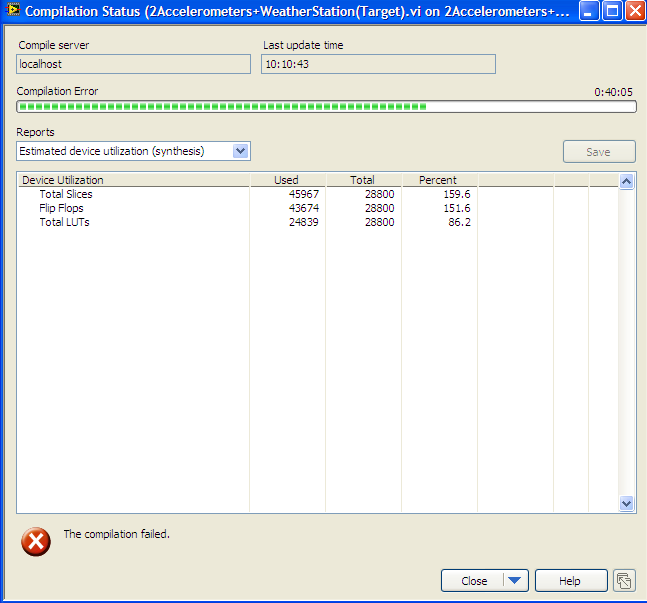

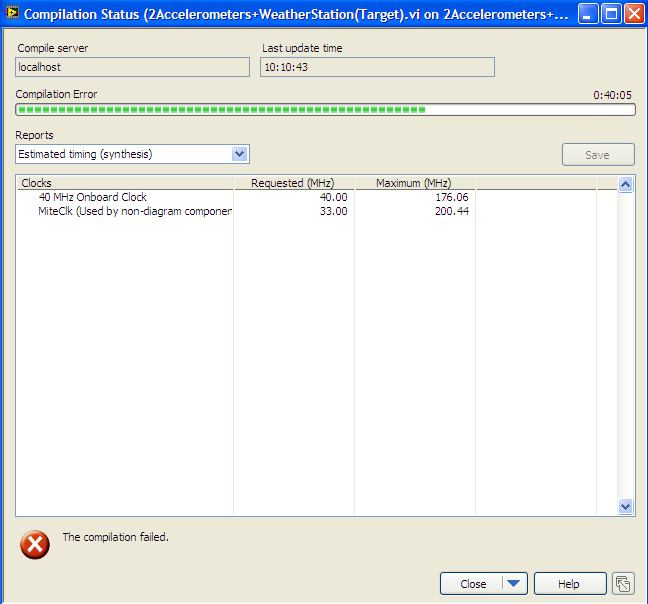

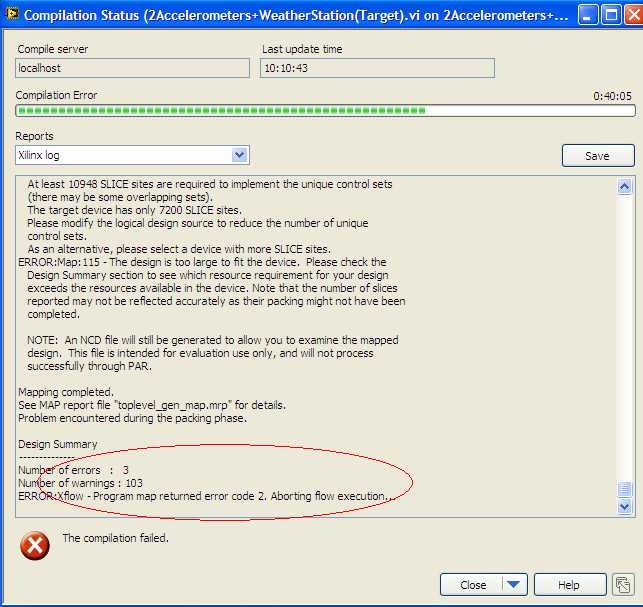

I met a problem when I tried to compile my target FPGA VI. Failed to compile for some reason any to halfway after start of the compilation. I post a few screen shots of the labview error information.

What causes this problem? How could I solve this problem?

Thank you very much!

Kind regards

masterwho

Also you have large networks on the Panel before the FPGA VI?

Or is there the great paintings inside the code?

If you can, put a piece of your code.

-

Hi all...

I think % CABLE_MODEM_HWIC-3-CONTROL_PLANE_FAIL: RBCP failure: failed to add the service ACE flow - type Ethernet not supported

on my 1841 which is currently set to L2L via internet cable. Anyone seen this before? I can't find anything on Cisco related to this.The tunnel rises and I got the same configs using DSL except interfaces are different. Thank you...My configs are below:crypto ISAKMP policy 10BA 3desmd5 hashpreshared authenticationGroup 2# address a.a.a.a isakmp encryption keyISAKMP crypto keepalive 20 periodicals!life crypto ipsec security association seconds 28800!Crypto ipsec transform-set esp-3des esp-md5-hmac xformCrypto ipsec df - bit clear!10 VPN ipsec-isakmp crypto mapthe value of a.a.a.a peerSet transform-set xformPFS group2 Setmatch address CRYPTO_ACL!interface cable-Modem0/1/0no ip addressBridge-Group 1Bridge-Group 1 covering-disabled people!interface BVI1IP address 98.x.x.x 255.255.255.224IP virtual-reassemblyVPN crypto cardHello DialerString,

I fear that the ACL is not related to the question, so I expect not to see anything in the debug output

Hope to help

Giuseppe

-

Regarding UDP Rx. custom map FPGA for PC

Dear Sir.

We are not able to receive the data in LabVIEW which is captured in WireShark. We pass the FPGA card data to PC. Here we use the UDP protocol.

We follow the procedure below to send and receive data :

- Side map FPGA:

- We get the PC ARP request.

- Then, we give the answer ARP for PC.

- Then, we receive a PC UDP packet.

- After that, we send a UDP packet to PC.

We monitor all frames with WireShark Analyzer.

Let me know the solution and fill in the gap.

Thank you best regards &,.

Chick S

The only thing I see is I think you mixed up of your ports. Looking at your OCAP paper, it seems that the FPGA (10.1.8.121) sends to the destination port 1234, but your VI of receiver UDP listening on port 1200. However, if you change the receiver port on the VI of UDP Rx, you get an error: I don't know if you will be allowed to open the same port twice (once in the TX, once in the RX). If this is the case, you must move the two functions in the same VI so that they use the same refnum UDP.

- Side map FPGA:

-

FDM: Import performance Tuning, where "import processes: Map" is more times that takes the report

Hi Experts,

FDM report shows the "import process: map ' activity is much more time during the import process completed by do from the web interface for a unique time period (file 1 month = 4 MB). Please suggest how I can improve it?

Thank you

Vivek

In this doc attached are details on parameters DB contribute to improve performance.

http://docs.Oracle.com/CD/E40248_01/EPM.1112/fdm_dba.PDF

A tip, I would also give is the importance of the order of mapping. Basically, if you like the mappings you should order based on volume. If a similar mapping affects a large volume of documents, you want to apply only the first. This allows to reduce the Recordset down over time so that the least used mappings go against the smallest possible demappe data set.

-

get the error: 1720-smart hdd imminent failure (failing attr:0 = |) when starting?

HP cpmpaq notebook 6710 model skuno:rj459av b

I am getting error 1720-smart hdd imminent failure (failing attr:0 = |) when starting.

Need to change the HARD drive or other needs please specify.

Can I replace it with new 500 0r 320 HD (like my perivious one is 120 GB 5400 RPM)?

If not then where I get the 160 GB HARD drive or less because of our days is hard to find this type of HARD drive, out service in the market.

Please give me as soon as.

Kind regards

Varun Pandey

Oracle DBA

Varun Pandey

Oracle DBAYou can use everything you can find on the market. Just be sure that it is a portable thickness 9.5 mm SATA HDD. The maximum size available is 1 TB. Here's the manual showing how to replace the drive.

http://bizsupport1.Austin.HP.com/BC/docs/support/SupportManual/c00911959/c00911959.PDF

I don't remember if the 6710 b has a connector on the connector sata on the standard black plastic drive but do not panic if the drive when you pull a link that seems different from that of a disk sata hard. There is a piece of plastic card black you need to remove the old drive and reuse. It can be put in place so that the sata connections just plug right into the motherboard.

This is a good deal on a 7200 RPM 320 GB drive:

http://www.Newegg.com/product/product.aspx?item=N82E16822152235

I won't use anything other that a disc of 7200 RPM... it offers a significant improvement in access to time and the boot file.

-

Driver position of Process Mapping

Hello

Please provide me with the syntax of the OMB for driver position of Process Mapping

Thank you and best regards,

VincentHi Vincent,.

for example, to add operator postmapping commandOMBALTER MAPPING 'MAP_NAME' ADD POSTMAPPING_PROCESS OPERATOR 'POSTMAP_OP1' BOUND TO PROCEDURE '/YOUR_PROJECT/DWH_MODULE/PROC_FOR_POSTMAP1';

Kind regards

Oleg -

LabVIEW FPGA failure with compiler Xlinx?

I'm in LabVIEW FPGA 8.6 with NOR-RIO 3.0.1 (to 8.6). When I compile a simple program, I get the notorious:

«Error starting compile step: make sure that a compatible version of Xilinx tools is installed in the location specified in the setup of LabVIEW FPGA.»

I checked the FPGA compile server and I ran the utility fixTlink.VI with no improvement. This produces two identical PC, neither one having a FPGA installed card.

Any ideas?

After further analysis, the problem was to be in our facility in LabVIEW FPGA 8.6. Using the correct Installer of NEITHER solved the problem.

This thread is now resolved.

-

Compilation of LabVIEW FPGA on crash RT cRIO 9082

Hello

I developed a project of NI VeriStand FPGA (see Project.png) for a target of 9082RT cRIO (which contains 2 cRIO: 9205 & 9264).

I have develop a piece of software code to run it on the chassis of RT cRIO 9082 because I never used this kind of front frame.

The problem appears when I tried to compile the FPGA.

Start the compilation, I see a pop-up (see Msg.bmp) and failed to compile (cf.). Details.bmp).

With the following error, I'm sure that the failure is not because of my code.

Can you help me?

I found the problem that comes from the installation of 2012 more develop.

When the FPGA module and 13.4 Xilinx tools is installed, the DLL 'LIBBz2.dll' (of the NIFPGA\...\Common\nt\Xilinx record 13.4 "is not copied in the following"C:\Windows\system32"folder.

After I manually copied this dll to the "system32" folder, I restart labview and the compilation was successful.

A. Kaszubiak

-

Violation of compilation-Timing error FPGA

Hi all

I've been LV around for years, but I am a complete newbie when it comes to FPGA. I'm working on programming for a 9651 (SOM) using the Dev kit. I'm starting by small steps, but already tripped. I have a simple VI which retrieves a value from a FIFO and passes it réécrirait a different FIFO. When compiling, it gives an error of timing violation, and I don't know how to study. The VI is attached.

If background for the curious... I'm working on the side of our application to signal processing. I'm passing data from a prerecorded TDMS file to a FIFO. I want to send the FPGA, treat it and send it back. Eventually, it will come of I/O, but for now, I just want to work on the processing of the signal. Before starting work, I thought I'd just make sure I can transfer data to the bottom and back. Once I get this job, I'll start to developing processing screw for between the two.

Thank you!

Hi thutch79,

You can specify the version of LabVIEW you use and implementing CLIP half bridge that you use for the IO DevKit?

It was a timing violation introduced between LabVIEW 2014 and 2015, given the way the compiler Xilinx handled VHDL which takes in charge the second port Ethernet on SOM. If you use a CLIP half bridge that has been generated before 2015 LabVIEW (as the example of the expedition which I think begins with a CLIP called "DevKit"), then you can get a timing error. There should be a second sample CLIP called DevKit2, I think, which was regenerated with compatibility for 2015 of LabVIEW and later versions.

This problem has been discussed here: https://decibel.ni.com/content/thread/42711

You can check your half-bridge CLIP in the project by ensuring that you have selected the version called DevKit2 if you have a version of LabVIEW FPGA which is 2015 or newer.

Kind regards

-

build books for Slot 1 cRIO module Profibus - FPGA, but fails to Slot 7

We have a Profibus cRIO module installed in a chassis cRIO-9024 and difficulties during the process of generation FPGA. Construction is very well when the project is configured for the Profibus module in Slot 1, but it fails with errors in Code generation, when the project is configured to Slot 7. I created a very simple pair of projects (attached) which illustrate the problem.

Error messages are "a generation of HDL code error has occurred" and "Terminal (to the) requiring a constant wired entrance to not constant or sources. A screenshot is included in the attachment.

Commenting on the second sub - VI ' CS_cRIO_PBM [7] FPGA_SPI_ReadWrite.vi "in Profibus_Slot7.vi allows the FPGA code build without errors. Tried the constants of wiring for the Subvi entries and other variations, but still failed to build.

I am aware that the documentation for the Profibus module recommends installation in Slot 1, but our client requires us to install in Slot 7.

Someone at - it understand the generation of Code errors that I receive?

(1) you use the old driver and this is expected behavior.

(2) the new driver will allow you to put the module in any location. Be sure to leave an empty slot next to him due to thermal considerations.

-

Oracle Form compile all active SQL rules fails

Hello

I finished the steps of Installation of the CCP.

Now, I'm in the steps of the Installation of the poles.

RCMP - rules of compilation of SQL, I clicked on "Oracle Form compile all active SQL rules" in the Tools menu bar.

And I checked the State "process is finished with the error. Here is the error log:

---------------------------------------------------------------------------

RCMP controls custom: Version: UNKNOWN

Copyright (c) 1979, 1999, Oracle Corporation. All rights reserved.

Module LAGENLIB: library to generate controls RCMP

---------------------------------------------------------------------------

Current system time is May 22, 2013 17:52:30

---------------------------------------------------------------------------

Variable source CLASSPATH successfully...

LAGENLIB: Input parameters are

LAGENLIB: Name of the library: LABRSQL

LAGENLIB: Connect str: jdbc:oracle:thin:@grc.4iapps.com:1541:GRCTEST

LAGENLIB: The library will be: /ebiz/applmgr/apps/apps_st/appl/xxlaapps/12.0.0/bin/LABRSQL.pld

ebiz/applmgr/Apps/apps_st/Appl/xxlaapps/12.0.0/bin/LAGENLIB. PROG: line 64: LAGENLIB: command not found

LAGENLIB: Library Generation failed

LAGENLIB: Quit smoking with the error...

/EBiz/applmgr/apps/apps_st/appl/xxlaapps/12.0.0/bin/LAGENLIB

Program exited with status 1

---------------------------------------------------------------------------

Options, AutoComplete, the request for enforcement.

Size of the output file:

0

End of query options AutoComplete.

---------------------------------------------------------------------------

Simultaneous request ended

Current system time is May 22, 2013 17:52:30

---------------------------------------------------------------------------

And I tried the Document link for the solution below. But still am experiencing this problem.

Compilation of SQL is any mistake when CCP 7.3.1 is installed against database 11g [1078979.1 ID]

Please suggest me to fix this problem.

Concerning

Kumar VThank you very much.

The problem has been resolved.

Solution.

I run the script laconfig.sh once again, then complie all active sql rules, its normally filled.Thanks Yasser.

-

acquisition of data and processes in FPGA

Hello!

In FPGA, I am trying to acquire analog data (0 ~ 10V) with a specific time clock rising edge of each digital pulse encoder.

I went to get the data on the front, but I don't know how I'd keep th and i + 1 th data.

(Frequency of data is less than 250 kHz)

I have the cRIO-9074, NI 9411 (encode), NOR 9205 (module I),

data

1st, 2nd data, data 3rd 4th 5th 6th 7th... I-1 th, I e, i + 1-th... 1200 e (approx.)

I need every sum of two consecutive data data 1st + 2nd, 2nd + 3rd, 3rd + 4th, l - 1 e + i Thess,... th + (i + 1-th)... 1199 th + 1200 e (about)

On the process of two consecutive sum.

[i - 1 e + i th] / [a value] + [the other i e amount of different data acquisition] = 1199 set of data (up to 1200 th data)

and then

all data across data (data from 1199) will be worth.

Thank you very much!

All tips are welcome!

Sincerely,

Hyo

Looks like a simple feedback node will do the trick.

-

FPGA error: failed to create the C Series module

I use sbRIO 9631 with LabVIEW 2012, as well as the FPGA 2012 module. Everything worked fine until yesterday, I got this error when creating a new FPGA project.

«LabVIEW FPGA: an error has occurred loading the VI on the FPGA device.» Check that the target is connected and powered and that the target resource is configured correctly.After ignoring this error, I can create any VI in the FPGA target, compile it and it works but can not do anything with host one. MAX configurations show so no error.

I have attached snapshots for convenience.Note: This sbRIO came with a DVD of LabVIEW 8.6 and similarly associated modules version. I had been using this version for a year. Then I got LabVIEW 2012 with the last modules and now facing this error.

Hi NapDynamite,

You should not need to uninstall your previous version of LabVIEW for the development of your PC.

You can see what version of NOR-RIO you have installed on your sbRIO? You can view it by selecting the sbRIO under "Remote Systems" of MAX, and then by selecting the category of software. You may need to update the version of NOR-RIO that is installed on the sbRIO.

You can try this first?

Kind regards

-

The project-centric issue of peer to Peer with an external compiler in LabVIEW FPGA

Hi all

FPGA OR Version: 14.0

I have an application developed in LabVIEW interfacing FPGAs developed in LabVIEW FPGA making of peer to peer Communications.

Everything works fine.

I try on the port to Visual Studio 2013 (on the same PC) and am able to communicate with the FPGA very well using the C API.

However, I have a problem now with the help files or the peer supported external compiler peer.

I get these errors:

1. cannot open the file source 'PublicIncludes/nistreamCommon/prefix.h '.

2. impossible opening the file source 'PublicIncludes/nistreamCommon/postfix.h '.

in

c:\Program Files (x 86) \National Instruments\Shared\ExternalCompilerSupport\C\include\nip2p.h

in my project...

I looked in the folder c:\Program Files (x 86) \National Instruments\Shared\ExternalCompilerSupport\C\include\ and the PublicIncludes\nistreamCommon folder does not exist.

What I am doing wrong?

Hello!

It seems that you have worked with another engineer of Applications on this issue. For the love of documents, the nip2p library is not supported in CVI. There has been cases where users were able to get this work to comment on the two header files.

Thank you!

Maybe you are looking for

-

When moving in different time zones, how to keep timely events?

When I put an event in PST at the exact time in which it will happen and then change the time zone, the event moves to another time. I have not shot time zones. Some events move and others keep time. How can I get all the events to keep time?

-

Configure a real-time desktop PC

Hello I'm so hard to convert a PC target RT tring. And I have a big problem. RT target is delivered successfully in Safe Mode, I can add some softwars on it but some softwars come with an error while adding: "the password you typed is incorrect. ..."

-

I'm not a computer whizz and now I fear I can have made a big mistake when I thought I was doing something safe. So here's the story, I wanted to do a little more space on my drive hard because I don't have but a small memory netbook. After the usual

-

Windows backup in windows vista home base provides space on disk D:\ limited.

before my question make a windows to the top, I have little space on the D drive.So I did a backup on my windows Home Basic computer. It took 10 DVDs to catch up the back.This must have backed up all the files on my computer. When I do a back up agai

-

Hi all Y at - it no reference document for the programming of the guidelines for the development of BB. That will explain the naming conventions and best practices. Thanks in advance, Sandeep