LabVIEW FPGA code changes

Hello

I'm working on 802.11 application, I tried to change the FPGA code.

I really need to compile all the code after changes? or just save the VI to observe the effects of the change.

Yes, LabVIEW code must be compiled using the FPGA Toolbox after you make all the changes. I think the only exception is when you run mode simulated on your PC.

Tags: NI Software

Similar Questions

-

LabVIEW FPGA: Problem compiling look-up Table

Current versions of software:

LabVIEW 2014 SP1

LabVIEW FPGA 2014

Xilinx Vivado

I'm having a huge problem in trying to compile my LabVIEW FPGA code.

Some recall of the code:

It's all in a SCTL.

I am streaming in a FIFO DMA and comparing it with the values previously stored in the shift registers (which are initialized to 0 at the start of the loop) in the SCTL.

The results of the comparison are then piled into a U16 and loaded into a lookup table (I use the LUT - 1 d), and I'm so help this LUT to decide what value will be charged to travel to record for the next iteration of the loop, which, in any case, would be either the current values of the flow, or the post previous registry value.

(It's a triage loop)

I am able to run very well in simulation mode code, but when I try to compile, I get this error:

"The selected object has a built-in shift register that makes the output on a particular loop iteration correspond to the entries in the previous iteration."

Connect the outputs of the object directly to a minimum number of nodes of Feedback or uninitialized shift registers. You cannot connect the outputs to another object.

See using LabVIEW for more information on the objects with registers embedded offset. »

Someone at - it ideas why this happens, and what might be the possible solutions?

I'm tempted to break it down into separate loops, but I prefer not to because it is now a loop (and working in my simulation).

I found my problem.

Any time that a LUT is in a chain shift register, it cannot:

1. be part of a string of shift register that has a variable initialized

2. follow-up to no decisive structure, like a box structure.

I just moved the position of LUT and it works.

-

How to import codes Verilog in LabVIEW FPGA?

I tried to import the Verilog code by instantiating followed education in http://digital.ni.com/public.nsf/allkb/7269557B205B1E1A86257640000910D3.

but I can still see some errors when compiling the file VI.

Test file simple Verilog is as follows:

==============================

module andtwobits (xx, yy and zz);

input xx, yy;

output reg zz;always start @(xx,yy)

ZZ<= xx="" &="">

end

endmodule==============================

and after you follow the above link, we have created the instantiation as file

==============================================

Library ieee;

use ieee.std_logic_1164.all;mainVHDL of the entity is

port)

xxin: in std_logic_vector;

yyin: in std_logic_vector;

zzout: out std_logic_vector

);

end mainVHDL;architecture mainVHDL1 of mainVHDL is

COMPONENT andtwobits PORT)

ZZ: out std_logic_vector;

XX: in std_logic_vector;

YY: in std_logic_vector);

END COMPONENT;Start

ALU: andtwobits port map)

ZZ-online zzout,

XX-online xxin,

YY-online yyin);end mainVHDL1;

==============================================

Sometimes, we observe the following error when we put the flag on the output port.

ERROR: ConstraintSystem:58 - constraint

TNM_ChinchIrq_IpIrq_ms; > [Puma20Top.ucf (890)]: INST

"* ChinchLvFpgaIrq * bIpIrq_ms *" does not correspond to design objects.

ERROR: ConstraintSystem:58 - constraint

TNM_ChinchIrq_IpIrq; > [Puma20Top.ucf (891)]: INST ' * ChinchLvFpgaIrq * bIpIrq. "

does not match design objects.and Interestingly, if we remove the indicator from the port of exit, he sucessfully compile on the LabVIEW FPGA.

Could you take a look at and please help me import Verilog to LabVIEW FPGA?

I followed the basic steps of the instantiation on the link above, but still it will not work.

Please find the attachment for all files.

-andtwobits.v: original file from Verilog

-andtwobits.ngc: file UCS

-andtwobits.vhd: VHD file after translating a simulation model

-mainVHDL.vhd: master of the instantiation

Since there is no sample file for Verilog (VHDL file, there but not for Verilog), it's a little difficult to do simple execution on LabVIEW FPGA, even for examples.

Thank you very much for your support, and I'm looking forward to seeing all your help/answer as soon as possible.

Records,

The best instructions we have for integration Verilog IP in LabVIEW FPGA can be found here: using the Verilog Modules in a component-level design. My suspicion is that you did not uncheck the option 'add the IO buffers' in the Xilinx ISE-specific Options parameter when running XST (see page 8 of the .pdf)

-

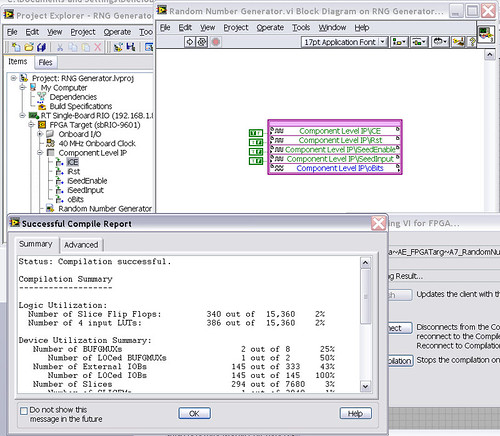

LabVIEW FPGA CLIP node compilation error

Hello NO,.

I work on an application for my Single-Board RIO (sbRIO-9601) and faced with a compile error when I try to compile my FPGA personality via the ELEMENT node. I have two .vhd files that I declare in my .xml file and all at this point works great. I add the IP-level component to my project and then drag it to the VI I created under my FPGA.

Within the FPGA personality, I essentially have to add some constants on the indicators and entries CLIP to my CLIP out and attempt to save/compile. With this simple configuration, I met a compilation error (ERROR: MapLib:820 - symbol LUT4... see report filling for details on which signals were cut). If I go back to my VI and delete indicators on the output (making the output pin of the CLIP connected to nothing), compiles fine.

I've included screenshots, VHDL and LV project files. What could be causing an indicator of the output of my VI to force compilation errors?

Otherwise that it is attached to the output ELEMENT, a successful compilation...

After that the output indicator comes with CLIP, compilation to fail...

NEITHER sbRIO-9601

LabVIEW 8.6.0

LabVIEW FPGA

Windows XP (32-bit, English)

No conflicting background process (not Google desktop, etc.).Usually a "trimming" error gives to think that there are a few missing IP. Often, a CLIP source file is missing or the path specified in the XML file is incorrect.

In your case I believe that there is an error in the XML declaration:

1.0

RandomNumberGenerator

urng_n11213_w36dp_t4_p89.vhd

fifo2.vhd

This indicates LV FPGA to expect a higher level entity called "RandomNumberGenerator" defined in one of two VHDL files. However, I couldn't see this entity in one of two files. If urng_n11213_w36dp_t4_p89 is the top-level entity, edit the XML to instead set the HDLName tag as follows:

urng_n11213_w36dp_t4_p89 Also - in your XML, you set the 'oBits' music VIDEO for output as a U32, however the VHDL port is defined as a vector of bits 89:

oBits: out std_logic_vector (89-1 downto 0)

These definitions must match and the maximum size of the vector CLIP IO is 32, so you have to break your oBits in three exits U32 output. I have added the ports and changed your logic of assignment as follows:

oBits1(31 downto 0)<= srcs(31="" downto="">

oBits2(31 downto 0)<= srcs(63="" downto="">

oBits3(31 downto 0)<= "0000000"="" &="" srcs(88="" downto="">Both of these changes resulted in a successful compilation.

Note: The only compiler errors when you add the flag because otherwise your CUTTING code is optimized design. If the IP is instantiated in a design, but nothing is connected to its output, it consumes all logic? Most of the time the FPGA compiler is smart enough to get it out.

-

Compilation of the variable results in LabVIEW FPGA

Hello. I would ask why LabVIEW FPGA generates different results of compilation for the same code. When I compile several times my code, the maximum speed and total changes bitfile slices generated according to the compilation, but I does not alter with the FPGA VI. In addition, is the precise relationship of compilation? Thank you

It's normal. The FPGA compiler starts to place pieces of code on the FPGA somewhat randomly and adjusts them until either the design adapts and responds to the criteria of the moment or there that the compiler determines that it cannot fit all the code and meet time constraints. The outputs that the FPGA VI generates when run will always be the same.

-

LabVIEW FPGA SP1 2012 & EVS1464RT FPGA IO

Hello

There seems to be problems with the new Labview FPGA 2012 SP1 in combination with an EVS1464RT embedded Vision system, which took place only after upgrading to SP1 2012 Labview:

- While trying to compile our code for the EVS1464RT FPGA or (Vision system embedded with e/s based on a FPGA Virtex-II FPGA) Xilinx tools (V10.1, since it's a Virtex-II FPGA) has reported an error saying that the compilation work has tried to set the property 'Data (output events)', which does not exist, so the Xilinx tools just quit with an error.

A complete uninstall and reinstall 'clean' do not solve the problem.

Research has shown that there is a property correct for Xilinx tools, called "done (output events)." An extended search in the Labview upwards 'incorrect data (output events)' some text files in 2 files "resource.xml" in the directories '...\National Instruments\LabVIEW 2012\Targets\NI\FPGA\IMAQIO\IMAQIO-1 "and '...\National Instruments\LabVIEW 2012\Targets\NI\FPGA\IMAQIO\IMAQIO-5' (and nowhere else).". " Change these 2 texts to 'Done (output events)' corrected the error and allowed to compile the code again.

- Another problem is that you can not start the VI FPGA-interactive (for example by clicking the Run button). This product just another error message saying that the VI '...\National Instruments\LabVIEW 2012\vi.lib\FPGAPlugInAG\IMAQIO-5\niFpgaOpenAndRun_IMAQIO-5.vi' could not be found (and there really is not anywhere on the hard drive).

The FPGA VI can be started from an another VI on the target host by using the function "Reference open FPGA". Then it works without any problems, so the bitfile has been obviously compiled correctly.

All of this worked out of the box without any problems on my old installation of Labview (before 2012 SP1 update).

The first problems now seems to be a simple typo, and using the function "Open FPGA reference" is a workaround for the second problem. But I'm very angry that National Instruments does not seem to test their software before releasing. A service pack should never break things that worked before.

Find these alternatives cost me 3 days, which, in my opinion, could be acceptable for open-source software, but not if you pay hundreds of euros per year for a "Standard Service program. For that kind of money, I expected NOT to test all the changes that they do well.

Best regards

Dr. Merlin Welker

Hello Mr. Welker.

First of all, thank you for your comments. I'm really sorry that you stumbled on this issue. Please let me give you some background information on it.

You are right that the update for the versions of service pack is to address reported problems and he should never break things that worked before. Unforunately, a change in LabVIEW FPGA exposed an underlying issue with e/s NOR-IMAQ driver FPGA compilation. We have identified this issue and addressed it in the Acquisition of Vision Software communicated in February 2013, including e/s NOR-IMAQ 2.6.1.

It is now available in the Update Service of NOR. We also found and addressed the issue with the FPGA Open running and run interactively in the thatsame release.

We recommend the upgrade to use the latest version of driver, whenever you upgrade from versions of LabVIEW, to ensure better compatibility between them. Please note that whenever you upgrade LabVIEW FPGA or Vision Acquisition Software, you should also recompile your LabVIEW FPGA projects.

While these issues were found and corrected in the latest version, we are now reminded our development and testing processes for future versions. Please accept our apologies for the inconvenience. National Instruments is committed to your satisfaction and to maintain your confidence in our products.

Thank you

Elmar

- While trying to compile our code for the EVS1464RT FPGA or (Vision system embedded with e/s based on a FPGA Virtex-II FPGA) Xilinx tools (V10.1, since it's a Virtex-II FPGA) has reported an error saying that the compilation work has tried to set the property 'Data (output events)', which does not exist, so the Xilinx tools just quit with an error.

-

Open FPGA references change to no. target when compiled with executable in time real start

Hello again you useful forum fans! I have a problem that I hope someone can give me a hand with.

I have a project that has a Windows component and a component of the target in real time, that are running on a hypervisor type NI PXI-8110 system. Communication both sides between them using shared variables.

On the real-time side, I have four FPGA targets who are reading and writing various analog and discrete inputs and outputs. I several periods loops which opens a reference to one of the FPGA targets during the first call, then pass this reference in several subVIs that read and write to panels prior to the FPGA. The loops the FPGA reference thus made available and reuse it in the next iteration through the shift registers. Each FPGA target has only a single reference open to him. One of the loops is using the FPGA reference directly and does not pass it in any subVIs.

It all works very well in the development environment, I can read and control inputs and outputs FPGAS via the front panel of the application of the side Windows. It also works very well if I start the game real time in the development environment, and run the code of windows as a stand-alone executable file.

However, when I compile the code in real-time in an executable startup and deploy it to the target, it does not work. I enabled debugging on the executable, and when I connect to it via the operation-> debug executable in the menu, I see an arrow broken at execution. Further investigation shows that each of the four open screw reference FPGA is now empty, the text under them is "no target" and the thread for reference on their part to my first Subvi is broken. I need your help to understand how to operate as it does in the development environment.

I followed the instructions of these two knowledge base articles to compile and download the bitfiles FPGA on the FPGA target and execute on start or restart:

http://digital.NI.com/public.nsf/allkb/39795847AC67296D862575FB0046944F

http://digital.NI.com/public.nsf/allkb/BC513C2A0DC29C89862574BF0002B0B9?OpenDocument

Open FPGA reference screw are configured for the FPGA to build specifications that I created for each target in the LabVIEW FPGA project.

I called technical support, NO phone, and yet were able to determine this one out, so additional "brownie" points if you do!

I would offer you the same no detailed screenshot that I have (I can't give more detailed code out because its owner, unfortunately), but apparently the forum doesn't like my image file, as I can't seem to load.

I would offer you the same no detailed screenshot that I have (I can't give more detailed code out because its owner, unfortunately), but apparently the forum doesn't like my image file, as I can't seem to load.Please let me know if you have any ideas regarding what is happening! I appreciate it.

Jon,

I'm always up for the challenge. Have you tryied recompile the FPGA VI that accesses the RT VI? I also suggest to try and open the bitfile instead of the FPGA VI. You run in dynamic mode (this is not a suggestion, it's just a question)? There is no difference if you try to open the FPGA VI reference outside the while loop, then past the reference to use inside the while loop without shift registers, then close the reference to the FPGA VI outside the while loop?

Let me know if these suggestions makes no difference.

-

How to measure the frequency of sampling (s/s) in LabView FPGA?

Hello

I am trying to find a way to measure the sampling frequency (s/s) during which I read from analog input in LabVIEW FPGA. I know that the sampling frequency is specified in the data sheet of the module HAVE, but I want to measure in LabVIEW.

Any suggestions?

A screenshot of the example code would be greatly appreciated

Hey phg,.

If you have some time loopand in this loop, you export a sample by iteration of loop via an I/O node. You can't out two samples on the same I/O node within an iteration, it's always one!

So if your loop takes 1 second to run you have a sampling rate of 1 Hz output. The same goes for sampling of entry. How long your loop takes to run can be calculated as explained above.

Samplerate [s / s] = 1 / [s] while loop

-

LabVIEW FPGA: Integration node clock wrong

Hello

I'm having some difficulties to understand how the clock is part of the node IP for LabVIEW FPGA and was hoping to get some advice.

What I try to do is to set up a digital logic circuit with a MUX feeding a parallel 8-bit shift register. I created the schema for this Xilinx ISE 12.4, put in place and can't seem to import the HDL code into an intellectual property node. When I run the VI, I am able to choose between the two entries for the MUX, load the output in the shift register, clearly the shift register and activate the CE.

My problem is that when I switch to the entrance of THIS, he should start 1 sec shift (Boolean true, SCR, High, what-have-you) in the registry once each clock period. Unfortunately, it instantly makes all 8 bits 1 s. I suspect it's a question of clock and here are some of the things I've tried:

-Specify the input clock while going through the process of configuring IP nodes.

-Adding an FPGA clock Constant as the timed loop.

-Remove the timed loop and just specifying the clock input (I'm not able to run the VI that I get an error that calls for a timed loop)

-Do not specify the clock to enter the Configuration of the IP node and wiring of the FPGA clock Constant to the clock input (I can't because the entry is generated as a Boolean).

-Remove an earlier version of the EC who had two entries up to a door and at ISE.

-Specify the CE in the process Configuration of the IP nodes.

-Not specify this in the process of setting up nodes IP and wiring it sperately.

-Various reconfigurations of the same thing that I don't remember.

I think I'm doing something wrong with the clock, and that's the problem I have. Previously, when I asked questions to the Board of Directors on the importation of ISE code in LabVIEW FPGA, a clock signal is not necessary and they advised me to just use a timed loop. Now, I need to use it but am unable to find an explanation online, as it is a node of intellectual property.

Any advice would be greatly appreciated, I'm working on a project that will require an understanding how to operate clocks the crux of intellectual property.

Thanks in advance,

Yusif Nurizade

P.S. I have attached my schematic ISE and the LabVIEW project with one of the incarnations of the VI. The site allow me to add as an attachment .vhd file, but if it would help I could just paste the body of the code VDHL so just let me know.

Hello Françoise,.

I spoke to the engineer OR this topic and it seems that it was sufficient to verify that your code works, by putting a wait function of 500 ms on the while loop to check that the registers responsible and clear. I'm glad that it worked very well!

-

LabVIEW FPGA: An internal software error in the LabVIEW FPGA Module has Unknown

Sir/Madam,

Note Labview 2012 SP1 installed about 2 weeks ago.,.

Accident occurred during the compilation of an fpga vi who worked satisfactorally in the past.

When I restarted and went to the message recomplile "LabVIEW FPGA: an internal software error in the LabVIEW FPGA Module" see attached picture of popup.

I reinstalled Labview in its entirety and backed out the changes I made to the vi but still get the same message.

Thanks in advance

Daryl

It turns out that the question was in the VI and not of LabView FPGA module as the message may indicate. I created a vacuum vi, cut and pasted items in this from the vi error and recompiled and it ran very well.

Somehow the vi has been corrupted internally.

Thank you it's fixed.

-

LabVIEW FPGA: Deploy fpga with host program

Hello people,

I develop using a pxi-7831R (FPGA), 7.1 LabVIEW and Labview FPGA 1.1.0. I wrote the fpga code and a host vi and they work well on my development computer. However, I need to create an executable file and take it to my development computer to another computer (which also contains a pxi-7831R), and I don't know how to do it.

Then I just build an executable from my host program and place the 'bit' fpga file in the same folder as the exe and copy it to the target computer, or what I need to somehow add the bit file to my build configuration?

Thanks for any help!

Chris

Hi chassan,.

In LabVIEW 8.x, the exe will offer the bitfile automatically. I imagine it works similarly in LabVIEW 7, but it's probably best that manually regroup you the bitfile in your build options.

-

Acquisition of data in LabVIEW FPGA

Hello

I'm working on LabVIEW FPGA where I need to acquire data from a source and take the average. One way to do that is to continue to add each new signal to the oldest f sum and then averaged.

However, I would like to keep all of the incoming values in a file and save it. But when I tried it doing so, it gives an error message saying "table size cannot be changed. With this constraint, I am unable to write the data to a table.

Please suggest.

Thank you.

You need different acquire data, pass it to the RT, then sign in here. Impossible to use build table the FPGA as FPGA will not allow dynamic allocation of memory like that. You must preallocate the table then use replaces the subset of the table. A better way is to use DMA FIFOs. Have a look at the FPGA examples in LabVIEW for data flow. Then, on the RT, you can simply add in your files logging functions.

-

Drivers Xilinx/Multisim and Labview FPGA

Where can I find drivers for my FPGA OR if I use Multisim/Xilinx and NOT of Labview? All the links I found are Labview be installed. However, the explicit manual FPGA indicates that you can use Multisim/XIlinx ISE in place.

OK, I tested just outside. The Driver of LabVIEW 2013 DEFB contains 2 separate components, the driver and Module FPGA support. If you run this installer, it won't check if you have LabVIEW FPGA installed unless you check the box for LabVIEW FPGA support.

I can change the text in the Installation Instructions to read "LabVIEW FPGA 2013 is required to install the LabVIEW FPGA Module Support component installation".

-

Error of timing in my fpga code

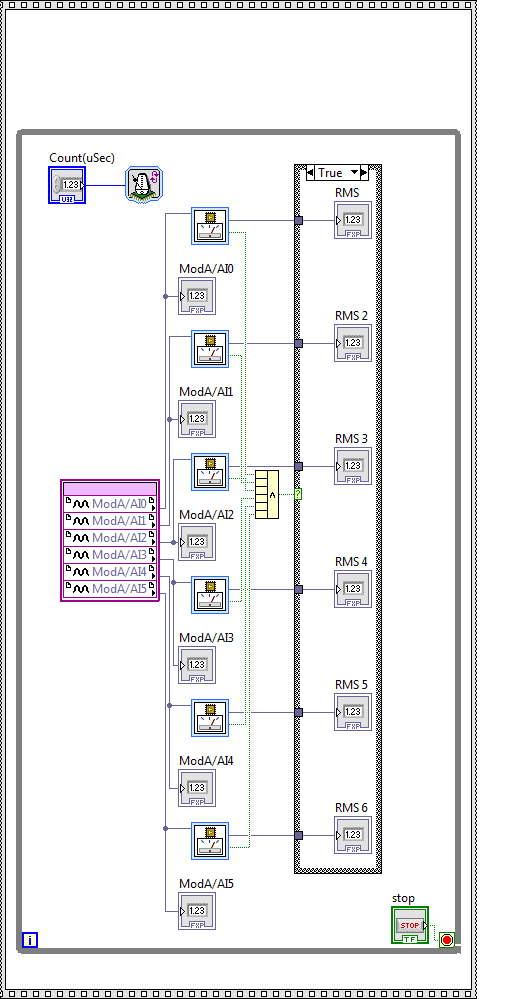

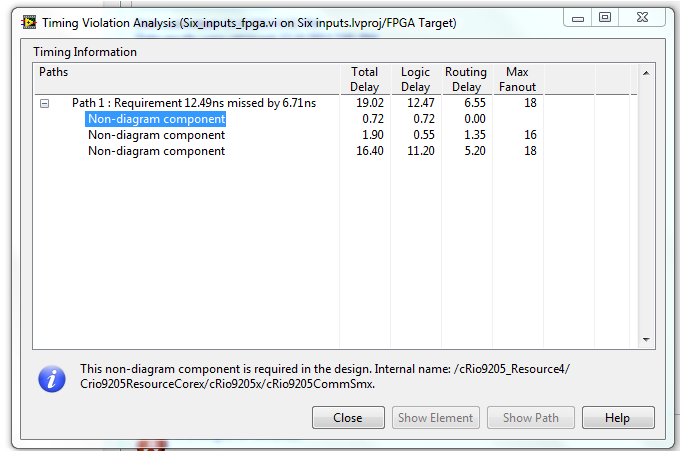

Hello everyone, I have attached an image with which basically indicates an error that I get when I compile my FPGA code. I am also attaching a photo of my code with it. I am a newbie in Labview FPGA and this code might not be effective way to achieve what I'm trying to accomplish. Basically what follows is the application.

I have a sbrio 9642 and I'm six analog inputs and I would get the effective value of these six signals to be as accurate as possible. The entries are pure sinusoids with a frequency of 60 HZ.

If anyone has questions about the code or demand, please post in this discussion. I will try to answer as soon as possible.

Kind regards

Kumar

-

FPGA code will stop when the code RT

I developed a FPGA code to manage a piece of hardware. It's the installer to read some default Panel control configuration values and then sit there constantly respond to signals input and output signal. The bitfile FPGA is written in flash to load FPGA memory and starts almost immediately. So far, everything is good.

Then I layered on the code of RT (cRIO-9075) system that opens a reference FPGA to the FPGA façade and allows me to follow a few indicators and change configuration settings and cause the configuration settings is changed be used by the FPGA. So far, it seems to work too when I run the RT code interactively (eventually there will be an interface for a host system).

The problem occurs when the code RT is ordered to stop. If you stop the RT code also, the judgment of the FPGA code and I will not stop the FPGA code. The RT code does not all calls to order the FPGA code to stop execution. When the RT code is stopped, the only thing she does in regards the link to the FPGA is to close the reference FPGA VI which was opened when the RT code was started.

What should I do to cause the code FPGA to continue to operate as the RT code is started and stopped?

I have to wait that I return to the office tomorrow to test this, but I think that this link has the answer to my problem.

http://lavag.org/topic/16412-confusion-regarding-FPGA-Deployment/#entry100294

It is said: "close FPGA VI reference. If you right click you have an option to close or by default close and reset. This means the VI FPGA is reset (read aborted in standard LV talking) when we close the reference. »

Maybe you are looking for

-

Time Machine and Motorola SB6141 cable Modem is to create an internet break

I had a SB6141 since I got cable internet 1/2014. I had hung by a former Airport Extreme Base Station - it was all good. I bought a time machine from Apple refurb > 6 months ago but < 1 year ago. I had injury disruptions of the internet - I only k

-

cannot turn off voiceover or access the iTouch

Sparked the iTouch. Time, date, etc are read. the slide to open the box goes to the camera when I try to drag. I managed to reach the area where I enter the code but nothing happens after that I entered the code. I tried to touch the original key

-

Hi guys I am studying a book of Labview and I'm stuck, making this example. I can't connect the output of the while loop. In the attachment, there is a JPEG file, explains my problem. Please help me...

-

I have a photosmart 7280 I used with windows for a year, I just got an imac with osx 10.5.6 I installed it and everything works except print I can print a test page but of other prints just stop in the queue, I uninstalled and reinstalled, I have res

-

Could not find 'Between windows' in my search menu

HelloI buy a version of windows 7 pro and I would install it.It does not install it... I tried first via the start menu, on the search screen, no upgrade of windows is now over I'm in the configuration panel, system, so I find an upgrade... There is