import VHDL FPGA in Labview

Hello

I have to import the VHDL code in Labview. I would like to know what the best solution what CLIP, integration IP node or node on HDL from the previous version of Labview if it is possible to use it.

Thank you

Hello

I think that these documents will help you to choose from, depending on your needs:

Difference between nodes CLIP and HDL

CLIP and the differences of node IP integration

Kind regards

Tags: NI Software

Similar Questions

-

decriptare codice vhdl generato da labview FPGA

Salve,

Quello che sto cercando di rates e di open a file vhd generato da labview FPGA during the United Nations VI, per vedere come viene scritto codice di compilaizione of it. Questo pole mi'd of poterlo confrontare con UN identico codice scritto directly in vhdl...

Salve,

non e possibile access al codice vhdl generato da LabVIEW FPGA compile durante.

LabVIEW e stato been proprio per evitare di codice vhdl texts scrittura/analysis.

-

import excel data to labVIEW, filtering and exporting to Excel

LabVIEW dear specialists,

I have about 2500 data each for acceleration and force stored in two excel columns of the worksheet as well as time data in another column. My problem is to purify my data of noise so I could generate thin sinusoidal signals for my thesis. I'm still new to labVIEW and I would like to ask for help to import my data from labVIEW, filter and exporting to Excel. Please help me. I enclose my data below. Thank you very much.

froebaruch

Hello!

These could be good starting points:

http://www.NI.com/analysis/Excel.htm

https://decibel.NI.com/content/docs/doc-8226

A few examples delivered with Labview, too.

Kind regards

Marco

-

What are the differences between LabVIEW and LabVIEW FPGA and LabVIEW RT

I need a comparison of LabVIEW, LabVIEW FPGA, and LabVIEW RT

Sorry, I misunderstood.

LabVIEW RT (LabVIEW Real-time) combines graphical LabVIEW of programming with the power of a real-time operating system, allowing you to create applications in real time.

-

How to import codes Verilog in LabVIEW FPGA?

I tried to import the Verilog code by instantiating followed education in http://digital.ni.com/public.nsf/allkb/7269557B205B1E1A86257640000910D3.

but I can still see some errors when compiling the file VI.

Test file simple Verilog is as follows:

==============================

module andtwobits (xx, yy and zz);

input xx, yy;

output reg zz;always start @(xx,yy)

ZZ<= xx="" &="">

end

endmodule==============================

and after you follow the above link, we have created the instantiation as file

==============================================

Library ieee;

use ieee.std_logic_1164.all;mainVHDL of the entity is

port)

xxin: in std_logic_vector;

yyin: in std_logic_vector;

zzout: out std_logic_vector

);

end mainVHDL;architecture mainVHDL1 of mainVHDL is

COMPONENT andtwobits PORT)

ZZ: out std_logic_vector;

XX: in std_logic_vector;

YY: in std_logic_vector);

END COMPONENT;Start

ALU: andtwobits port map)

ZZ-online zzout,

XX-online xxin,

YY-online yyin);end mainVHDL1;

==============================================

Sometimes, we observe the following error when we put the flag on the output port.

ERROR: ConstraintSystem:58 - constraint

TNM_ChinchIrq_IpIrq_ms; > [Puma20Top.ucf (890)]: INST

"* ChinchLvFpgaIrq * bIpIrq_ms *" does not correspond to design objects.

ERROR: ConstraintSystem:58 - constraint

TNM_ChinchIrq_IpIrq; > [Puma20Top.ucf (891)]: INST ' * ChinchLvFpgaIrq * bIpIrq. "

does not match design objects.and Interestingly, if we remove the indicator from the port of exit, he sucessfully compile on the LabVIEW FPGA.

Could you take a look at and please help me import Verilog to LabVIEW FPGA?

I followed the basic steps of the instantiation on the link above, but still it will not work.

Please find the attachment for all files.

-andtwobits.v: original file from Verilog

-andtwobits.ngc: file UCS

-andtwobits.vhd: VHD file after translating a simulation model

-mainVHDL.vhd: master of the instantiation

Since there is no sample file for Verilog (VHDL file, there but not for Verilog), it's a little difficult to do simple execution on LabVIEW FPGA, even for examples.

Thank you very much for your support, and I'm looking forward to seeing all your help/answer as soon as possible.

Records,

The best instructions we have for integration Verilog IP in LabVIEW FPGA can be found here: using the Verilog Modules in a component-level design. My suspicion is that you did not uncheck the option 'add the IO buffers' in the Xilinx ISE-specific Options parameter when running XST (see page 8 of the .pdf)

-

Import static library Wizard labview 64 pointer size is 32

I have labview 2009 sp1 64-bit on a 64-bit with windows vista64 bit computer. I use the Import Wizard to the shared library on a dll 64 bit with the header file provided.

I noticed that the header file shows some functions like the passage empty *. When the wizard generates the library call nodes and terminals vi it makes U32. Maybe miss me something here, but on a 64-bit computer, it should not be U64? I think that if the 64-bit dll tries to return a pointer that points to the address exceeds the limit of 32-bit, I could get into trouble here.

Is it an OR on the view or my misunderstanding?

Thank you

James G

From LabVIEW 8.6 (or was it 2009? I don't remember for sure), we have a 'size integer pointer' option for the call library node parameters. If the Import Wizard tries to wire an integer to an empty parameter * pass by value, then it should be to establish the type of the parameter to the size pointer value and make the wire/control itself an integer 64 bit (on all platforms). There is a limitation in our 64-bit support, because the Import Wizard is prior to this option (and our 64-bit version of LabVIEW). I will file a bug for her report.

-

Software FPGA with LabVIEW 2013

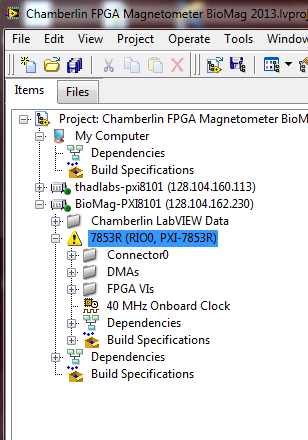

I have a system with a rotating computer "development" under Windows 7 and an NI PXI-1036 chassis with a PXI-8101 controller as well as a card FPGA PXI-7853R. Recently, I upgraded to LabVIEW 2011-2013 of LabVIEW. I kept LabVIEW 2011 installed just to make sure everything is still working on the new LabVIEW.

Now, when I open my project in LabVIEW 2013 Project Explorer, my FPGA comes with a warning triangle yellow next to him (see attached photo). The warning says:

"Software support for this target FPGA is not installed on the computer. You can view and copy elements into the project, but you can not compile any screw under the FPGA target, until you install support for the target. Refer to the documentation of specific material for more information on the proper drivers and for more information about the installation and configuration of the target FPGA ".

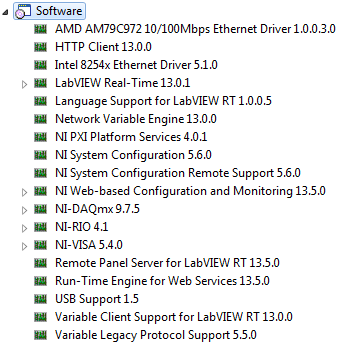

Regarding the installed software, I have LabVIEW SP1 of 2013, 2013 of LabVIEW FPGA Module SP1, SP1 of Module 2013 LabVIEW Real-time, and Xilinx Compilation tools 14.4. On the chassis of the TARGET (with the PXI-8101 controller), I have attached a list of installed software.

Interestingly, when I open the project in LabView 2011, no errors or warnings are present with the FPGA card. It is only under LabVIEW 2013 I see the warning. Did anyone see a glaring omission of software that could be the cause of LabVIEW raise this error? Thank you for your help.

Best guess is that're missing you the driver for your FPGA device. Try to install the latest version of NOR-RIO (or at least the version supplied on your 2013 SP1 install disks). Have you installed device drivers at the time that you have installed SP1 2013 LabVIEW?

-

How to import an image in labview

Dear Sir.

How can I import an image two bmp in labview and compare it... taking as reference and others as a sample...

Under the graphic palette and suond, you'll find two pallets more than imagews of the handle and the other image files.

Of those, you can do a pixel-by-pixel comapre.

Ben

-

Problem of memory, then I import a DLL on LabView 2010

Hello

I have a lot of problems with importing a file .dll on labview.

The blocks of import to the third of fourth function and sometimes a textbox appear (as you can see in attachment).

I tried with the import node, but it does not work (so maybe it's that I don't know how to use it really).

I don't really know how to import the entire library, and I am really stuck.

There is also the header and the dll as an attachment.

Thanks for your interest.

I didn't say it's impossible, but it is very likely well above your head. You probably have two options:

(1) to abandon this material and get a part that has a good support for LabVIEW.

(2) hire someone with a very good understanding about LabVIEW C interfacing and allow them to create a VI library and interface DLL for you.

Good luck

-

Parallel FPGA in LabVIEW/Multisim co-simulation

Hi guys, it is possible to put 3 or 4 FPGA modules in a model of LabVIEW and then simulate jointly with Multisim runs 1 model plant? I want to simulate a converter of solar by using multiple parallel FPGA (this part on LabVIEW) cores conducted multiple interacting with the grid inverter bridges (this part is the Multisim factory model).

Hey hacmachdien,

This should be possible. If you have the Control Design and Simulation toolkit, you can use the control and the Simulation loop to simulate jointly with Multisim after you have installed the co-simulation plugin that comes with Multisim. See here for more information.

If you encapsulate your LabVIEW FPGA logic inside a Subvi, you should be able to use these subVIs in control and the loop simulation. There are a few caveats with this. First of all, the rate for the LabVIEW FPGA SubVIs must be configured depending on how they will run in the actual hardware. For example if the Subvi is inside a timed Cycle simple loop that is configured for a 40 MHz clock, you will need to configure the delay for the Subvi 25 ns. You can set up the period right-click on a Subvi in control and Simulation loop, then go to the Subvi node installation. In this menu, you can set the type of operation to be discreet and then configure the discreet calendar. Another restriction is certain things will not be supported as I/O. You can usually work around this by leaving your IO on the next level of your app and just by passing the values in the Subvi through controls and indicators. Let us know if you have any other questions!

-

A UDP connection target FPGA with LabVIEW

Hello

I have an FPGA with Ethernet connected to my HOST PC, now I would like to connect the LabVIEW FPGA target and access to its records. Please suggest me.

Kind regards

Chetan

Hi Cheetah,.

don't know, because I do not know your format or the manual of your FPGA...

-

I installed 32-bit and 64-bit LabVIEW 2012 SP1 on Windows 7 X 64 computer. After that, I installed SP1 FPGA Module. While module FPGA completely installed in the 32-bit version and could develop projects fpga, FPGA interface has not installed the 64-bit version. Anyone had this before question?

The document 5WMF8NQ2 knowledge base says it's doable.

I have tried to repair the installed module, remove and then reinstall the module. Nothing helped me to get the FPGA interface on a 64-bit host VI. Any suggestions? Addition of the individual screws through the range of editing functions like a tedious process and the palette is not completely functional.

I solved the problem. Had to repair each driver separately for LabVIEW 2012 SP1 64 bit installed on the default drive. You may need to copy paste files to the folder that it installed in function.

-

Hardware implementation of the controller DMA using the FPGA and LABVIEW

Respected Sir/Madam

I am simulating the DMA using LABVIEW7.1 controller and I am fresher to this tool, please suggest me how to do this

You can go through the FPGA tutorial.

For specific information on DMA you can see this.

-

Error-63101 when executing the FPGA Interface C API Generator in LabVIEW 2012

I'm using LabWindows CVI 2012 and 2012 LabVIEW FPGA module. I try to use the FPGA Interface C API generator and I get the following error from a freshly generated .lvbitx bitfile. I use the local server compiles on my PC.

Error-63101

NOR-RIO: A valid .lvbitx bitfile is required. If you are using a valid .lvbitx bitfile, the bitfile maybe isn't compatible with the software you use. Determine which version of LabVIEW was used to make the bitfile, upgrade your software to this version or later, and then try again.

The problem occurs when executing CVI or LabVIEW. I was able to do this earlier when I was compiling the FPGA in LabVIEW with the API generator 2011 downloaded from the Web site.

A bit of weirdness in my setup, it's that I charged it off downloads from the website (latest files after 2012 NIWeek) rather than the normal distribution DVD. I installed LabVIEW, so NI RIO, then the Xilinx tools compatible with 2012. It works very well when you talk to the FPGA to a LabVIEW vi running on my Windows PC to the host.

Any suggestions?

Problem solved. I had to download FPGA Interface C API generator 12.0. It works now.

I would have thought that if a product was called on the menu in LabVIEW 2012, it would be prompted to upgrade to a compatible version, when I installed LabVIEW. The old version is not compatible with version 3.0 bitfiles, as identified on the following lines at the top of the .lvbitx file:

3.0 -

Learn how to run labview vi on fpga target

How to create a vi and execute on the target fpga on labview? What are the boxes to tools/modules required for the installation and the steps of creating a vi to execute on the target fpga

Hello Wrang,

If you want to program in LabVIEW FPGA targets, you need following:

-LabVIEW

-Drivers for supported target FPGA (OR-RIO)

-in some cases, you must have the LabVIEW Real-time module (for example to work with ComactRIO)

To start working with FPGA targets, I would highly recommend to go manual start-up of pit for specific device. In general it's pretty much the same for all targets, then you can take a look at Getting Started manual with CompactRIO and LabVIEW.

You can also find a lot of documentation or examples on our web site. For example, you can take a look at creating a FPGA and Application project.

I hope you enjoy to work with FPGA OR!

Kind regards

s9ali

Maybe you are looking for

-

How can I disable the auto-hide known file attachments and why are they always about 10 Web pages where I have to download something when I use mozila firefox? Windows computer

-

Why work on my imac osx 10.8 picassa used

After downloading I tells me that it won't work on this architecture.

-

in the Exec.vi system call stack overflow

Hello I have on dos application which I call you for a specific task through the entrance to the command line for system exec.vi... problem that I get to crash dos application without completing the task... I checked with the release of vi and he say

-

VPN connectivity and access software

Having records with XP machines connecting to windows server 2003 via VPN OK, but then cannot access software.

-

Disable install on the new computer

My old laptop has a fried GPU, and is not worth the money to fix it. I recently got a new laptop and I wanted to put my programs adobe on this, but I can't open my computer to turn them off of my old laptop. Is there a way I could disable any other