IP integration node

Hello

I loocked through many positions and searched in many materials, but could fins no answer to my problem.

I have my using the LabVIEW 2011 IP integration node.

For sbRIO9642, I tried to integrate an IP synthesized for x3s2000 FPGA from Xilinx ISE as ngc netlist file.

I always got error:

Annotation of the constraints to the design of the FCU, file 'toplevel_gen.ucf '...

Set associations of constraint...

Associations of constraint checking...

ERROR: ConstraintSystem:59 - constraint

PADS (mIoHWord_n) PADS(aIoInt*) 0 NS; > [toplevel_gen.ucf (375)]: BUFFERS

'mIoHWord_n' not found. Please make sure that:

1. the design element specified actually exists in the original design.

2. the specified object is spelled correctly in the file source of constraint.

It seams there are evil somethning in the intermediate file of constraint.

Cam anyone help me understandit is correct integrate the ngc netlist in LabVIEW FPGA.

Thank you

Manuk.

Hi Manuk,

It seems to be more information about this error on the Xilinx website in resources of NOR. Check out this link for more details. To make sure that your VHDL is in the correct format for an IP node, follow the steps described in this document.

Tim W.

Engineering applications

National Instruments

Tags: NI Software

Similar Questions

-

LabVIEW FPGA: Integration node clock wrong

Hello

I'm having some difficulties to understand how the clock is part of the node IP for LabVIEW FPGA and was hoping to get some advice.

What I try to do is to set up a digital logic circuit with a MUX feeding a parallel 8-bit shift register. I created the schema for this Xilinx ISE 12.4, put in place and can't seem to import the HDL code into an intellectual property node. When I run the VI, I am able to choose between the two entries for the MUX, load the output in the shift register, clearly the shift register and activate the CE.

My problem is that when I switch to the entrance of THIS, he should start 1 sec shift (Boolean true, SCR, High, what-have-you) in the registry once each clock period. Unfortunately, it instantly makes all 8 bits 1 s. I suspect it's a question of clock and here are some of the things I've tried:

-Specify the input clock while going through the process of configuring IP nodes.

-Adding an FPGA clock Constant as the timed loop.

-Remove the timed loop and just specifying the clock input (I'm not able to run the VI that I get an error that calls for a timed loop)

-Do not specify the clock to enter the Configuration of the IP node and wiring of the FPGA clock Constant to the clock input (I can't because the entry is generated as a Boolean).

-Remove an earlier version of the EC who had two entries up to a door and at ISE.

-Specify the CE in the process Configuration of the IP nodes.

-Not specify this in the process of setting up nodes IP and wiring it sperately.

-Various reconfigurations of the same thing that I don't remember.

I think I'm doing something wrong with the clock, and that's the problem I have. Previously, when I asked questions to the Board of Directors on the importation of ISE code in LabVIEW FPGA, a clock signal is not necessary and they advised me to just use a timed loop. Now, I need to use it but am unable to find an explanation online, as it is a node of intellectual property.

Any advice would be greatly appreciated, I'm working on a project that will require an understanding how to operate clocks the crux of intellectual property.

Thanks in advance,

Yusif Nurizade

P.S. I have attached my schematic ISE and the LabVIEW project with one of the incarnations of the VI. The site allow me to add as an attachment .vhd file, but if it would help I could just paste the body of the code VDHL so just let me know.

Hello Françoise,.

I spoke to the engineer OR this topic and it seems that it was sufficient to verify that your code works, by putting a wait function of 500 ms on the while loop to check that the registers responsible and clear. I'm glad that it worked very well!

-

[Labview FPGA]: block of memory use Xilinx HDL integration node

Hello

In my project, I would be developed my own VHDL module and integrated in my project of LV FPGA with a knot of integration.

But for an evolution of my code, I wonder if it is possible to use in my own code VHDL, Xilinx library (as a block of memory).

Thank you.

You can use any Xilinx IP (or IP and others) in your external code. For example, if you generate a block of memory using block memory generator you can instantiate this IP in your own VHDL.

-

Integration of IP node: VHDL + LAVIEW FPGA

Dear members

can I use a library set by the user or a parcel inside the IP integration node?

for example library that contain a function for fixed operations in comma?

As

Library IEEE;

Use IEEE. STD_LOGIC_1164.ALL;Use mustafa... pkg

Unfortunately, there is no way to directly access a block of memory of LabVIEW FPGA and an IPIN node. You will need to file a read/write memory next to your IPIN node node and manage lines of coordinates and data of your IPIN node as ports.

-

Integration of IP node evil in LabVIEW FPGA

Hi all

I am having trouble with the integration of LabVIEW FPGA IP option and was hoping someone could shed some light here.

I use a simple VHDL code for a bit, 2: 1 MUX in order to familiarize themselves with the integration of IP for the LabVIEW FPGA.

In the IP properties of the context node, the syntax checking integration says:

ERROR: HDLParsers:813 - "C:/NIFPGA/iptemp/ipin482231194540D2B0CC68A8AF0F43AAED/TwoToOneOneBitMux.vhd", line 15. Enumerated value U is absent from the selection.

but I'm still able to compile. Once the node is made and connected, I get the arrow to run the VI but when I do, I get a build errors in Code Pop up that says:

The selected object is only supported inside the single-cycle Timed loop.

Place a single cycle timed loop around the object.

The selected object in question is my IP integration node.

I add a loop timed to the node, but even if I am able to run the VI, it nothing happens. the output does not illuminate regardless of the configuration.

I would say that I tried everything, but I can't imagine would be the problem might be at this point given that everything compiles and the code is so simple.

I have attached the VI both VHDL code. Please let me know if any problems occur following different boards of the FPGA.

Would be really grateful for the help,

Yusif Nurizade

Hey, Yusif,.

Looks that you enter in the loop timed Cycle and never, leave while the indicator of Output never actually is updated. Try a real constant of wiring to the break of the SCTL condition. Otherwise, you could spend all controls/indicators inside the SCTL and get rid of the outside while loop. You can race in the calendar of meeting bad in larger designs without pipeling or by optimizing the code if you take this approach, however.

-

Hello

I'm trying to generate a sine at 13, 56 MHz on a 5641R. I managed to do it on the host, but now I want to create this on the FPGA, because after I want to achieve a modulation to make RFID. And I need to have all the code in the FPGA.

Does anyone have any idea how I can do this, or an example?

Thank you

Hi Simon,.

You can use Xilinx core generator and IP integration node to create a DDS based waveform or you can create it using LabVIEW FPGA. The LabVIEW FPGA tutorial also explains how to use a LUT with a sine wave, which if you will use only a single frequency can be a simpler way to go.

-

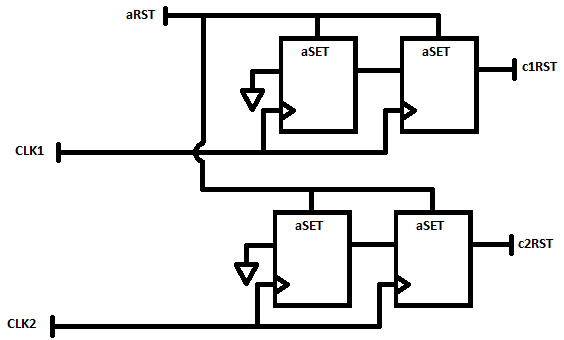

How the resets are generated in LabVIEW for FlexRIO

All,

My background is VHDL and Verilog for FPGA and ASIC implementations. I guess LabVIEW has a point, an only synchronous reset to all of its logic. I create a design that is going to be sections of VHDL IP, through IP integration node is instantiated. When writing to the top of my spec, I need to describe how a reset is spread to all the flops in the design that will be peer-reviewed of accuracy of the results. I need to understand exactly how LabVIEW handles resets to other areas of the clock.

A simple case is the following: I have a 50 MHz external source synchronous data interface and will be a limited treatment of data in this area of 50 MHz using an IP integration node. This IP is designed to have the flops to reset synchronous on the 50 MHz clock.

Separately, I have my most of my treatment and storage to the host (via DMA FIFO) in a field of 100 MHz clock, derived from the clock of 40 MHz I base I must transfer data from 50 MHz to 100 MHz using a FIFO. This treatment at 100 MHz contains a floating-point operations that are reset to zero synchronously to the field of 100 MHz.

In this scenario, you see I have two areas of clock with synchronous resets. I need to understand how LabVIEW FPGA create reset signals which are entries to my integration IP nodes, in order to understand if I need to incorporate any reset synchronization within my VHDL circuits.

Thanks for any help and if you need further details or context, please let me know and I find out additional details.

-Jim

Hey Jim,.

So, option 2 then... in this case, you are looking at a signal of asynchronous reset and must realize in your VHDL similar to the following to ensure that your resets are say synchronously.

-

Using of FPGA VHDL IP and analog output

I use a system with Labview 2014 PXI. I've got Labview FPGA to program and run the card PXI-7854R.

I have the VHDL Code I want to use to control an analog output of the card. I use the IP integration node for this now but I also tried it making the process CLIP and still have not been successful. The problem that arises is that the IP integration node must be in a timed loop, while the analog output indicates that it cannot be put in a timed loop. Is there a way to provide an output of VHDL analog outputs of the card?

I tried to embed a loop timed within a while loop, but it still does not work.

I can't download the VI due to the policy of the company, but suppose I'm generating a sine wave in my VHDL code which must lead to the analog output of the card (the actual wave is company owner information but it is generated by a glance to the top of the table as a sine wave VHDL would be).

In an attempt to work the problem I retried import CLIP of the HDL code in a new project in Labview and VI. I'm still not sure about why it did not work with each other when I tried it.

For anyone who seeks to solve this problem:

I basically used this tutorial for the process CLIP: http://www.ni.com/tutorial/7444/en/

It also explains the differences between the CLAMP and the IP integration node.

-

How can I import Verilog code in LabVIEW FPGA? I understand how to import the VHDL code by using a CLIP or IP integration node, and I wonder if there is a possible method to import the Verilog code.

Thanks in advance!

You can import verilog in labview by generating a netlist from verilog giving you a UCS or edif file depending on whether you use ISE or Vivado respectively.

From there, you can try directly imported the netlist labview using a node IP integration or you can wrap it in VHDL and create a CLIP of it. I recommend the latest, but we invite you to try to be.

To generate the netlist you will need your own copy of the OCDS Xilinx. Xilinx provides documentation on how to generate maps using their tools.

-

Hi, I created a new CI web service based.

But when I use the URL generated in the browser I get after error message.

"< SOAP - ENV:Envelope xmlns:SOAP - ENV="http://schemas.xmlsoap.org/soap/envelope/">"

< / IBResponse >

< / details >

< / SOAP - ENV:Fault >

< / SOAP - ENV:Body >

< / SOAP - ENV:Envelope >

Could someone help why this error occurs.

I understand that it is a question of the user name password

But where should I change or seek to correct this error.

Also when a web service is created on a CI can I overwrite or remove the system.

PeopleTools > Integration Broker > Configuration of integration > nodes

-Search for ANONYMOUS node

-Make sure that the default user Id ' on the ANONYMOUS node has access to all the service operations in respect of the IB_UTILITY service.

S ' ensure that the "authentication" is set to 'none '.

If you want to remove a WSDL, Service, operations, Message Service, schema, etc., you can use the following Administration Page:

PeopleTools > Integration Broker > Service utilities > Administration of Service

Let us know if this solves your problem. Thank you!

-

Process Scheduler running SQR report gets the Client HTTP response Code 401 Unauthorized error

People,

Hello. I'm under PeopleTools 8,53 Oracle Linux 5 with Oracle 11 g 1 material database.

Process scheduler run reports SQR and get the error message as below:

Error of the client Http Response Code: 401 - non authorized. Transfer HTTP error.

My report node information is below:

URLID: http://ip_address:port/p/psreports/ch

Home directory: /psreports

Resource URI: SchedulerTransfer/ch

Login ID: PS

Password: mypass

PeopleTools > IntegrationBroker > Configuration of integration > nodes: authentication option is selected password.

The 2 roles, ReportDistAdmin and ProcessSchedulerAdmin are granted to the user PS

Someone tell the error above due to incorrect or misspelled path for report repository in the configuration.properties file.

I see no error in my configuration.

My question is:

Can any help folk to solve 'Error Http 401 - transfer HTTP error response Code' unauthorized customer?

Thanks in advance.

I think there might help:

E-RD: transfer report error: Client Error Code: 401 - Unauthorized (63.59) (Doc ID 623250.1)

E-RD: what are the steps to configure basic authentication for the repository of reports on PT 8,4 x using Weblogic? (Doc ID 970572.1)

Also if you use this with test the load on load balancer balancer.

Kind regards

RAM

-

WebCenter spaces: content display model Presenter for the image gallery

Hi all

I use 11.1.1.6 Webcenter spaces

I need to create a custom content presenter display model where a folder is chosen by the moderator. And all the files it contains will be shown as an album in a drop down.

Whenever the user selects any album in the drop-down list, the images inside this album should be below in a thumbnail.

I've set up two models one for the drop-down list and others to show images.

I just need to know how can I use the two together. And how the selection of an album in the drop-down list should change the images?

Should I call 2nd model presenter content from 1?

Help, please.

Kind regards

Deepak

Hello.

I have a better approach:

- Store in a variable of limited scope, the folder selected in selectOneChoice.

- Use the cmfn:searchNodes function to retrieve the folder nodes

- Use the list of nodes with dt:contentTemplate.

Information on the use of cmfn:searchNodes:

Basically, he's waiting for the name of your repository of the University Complutense of MADRID and a CMIS query that must be built using the information in your file or a path.

The CMIS query will have to be something like the following example (he gets all the contents of the folder with xCollectionId =

988901828852000401SELECT * FROM cmis:document WHERE IN_TREE('/ucm/IDC:Folder/988901828852000401')Retrieve a collection of content nodes by CMIS query, specifying the maximum number of nodes to return. searchNodes oracle.webcenter.content.integration.servlets.functions.NodeRetrievalFunctions oracle.webcenter.content.integration.Node[] searchNodes(java.lang.String, java.lang.String, java.lang.Integer)

]]> -

SQL script to update the Peoplesoft database information

Hi all

I'm a new DBA for a charity running both PS financials & HR which often must create test, training and instances of dev of our production environments. Doing so currently requires a number of manual steps to update the different nodes and paths to those required for the new instance, and naturally I did not become a DBA to do manual work ;-)

I'm looking for these steps, but the schema PS script being what it is, I'm not having much joy to find where relevant data could be. If someone had a script to do something similar, or could point me in the direction of the tables, I would be extremely grateful. The kind of things that we currently do through the interface are:

PeopleTools > Integration Broker > Configuration of integration > nodes

PeopleTools > Security > security objects > Single Sign-on

PeopleTools > Public Services > Administration > URL

PeopleTools > Integration Broker > Configuration > Quick Setup > Integration Broker areas

PeopleTools > Portal > node definitions

PeopleTools > the Ren Server Configuration > Ren Server Cluster

We are currently running MS SQL Server, but all the PL SQL scripts would be great - I just need to know what are the tables contain the data.

Thank you very much

AndyWell, it is very dependent on version Peopletools.

An easy way might be to open the corresponding page that you speak, and then display the definition of page and the associated record. At least that is what I use to do.

Then, update you the table background and see if she takes your new values.To be brief, here is an excerpt of these tables (non-exhaustive list, PT.48):

Node of single sign - we built: pstrustnodes

Scheduler process definition: ps_serverdefn

Run the command: psprcsruncntl

Message channels: pschnldefn

The e-mail table of contents: psapmsgpub *, psapmsgsub *, psapmsgarc *.

Definition of message node: psmsgnodedefn

URL: psurldefn

Definition of employment: ps_prcsjobdefn

OPRID (e-mail address): psoprdefn

...Then fill out your own list with the method that I gave above.

Nicolas.

-

Integration IP node: impossible to link design

I am unable to generate support files when you import a VHDL file in node IP integration. I've seen people having the same problem, because they used a non supported OS but my OS is supported by Vivado 2014.4.

I have:

OR LabView 2014 with all modules and the latest updates installed

Xilinx Vivado 2014.4

8.1 Windows 64-bit (which is sipported by labview)

I get the following error:

Waiting for 2 sub-compilation (s) at the end...

ERROR: [XSIM 43-3238] cannot link design.

Generated in vain IP. Your source file may not work for the FPGA family (es) that you select. Difficulty errors or warnings above and generate the IP address again or return to the previous page to reselect FPGA family support.It is worth mentioning that I selected that one FPGA (zenq) family that vivado takes in charge. The code that I'm importing is correct and very short. Just a test of LED that worked well in simulations. What is causing this problem and how my I solve this problem?

Hi aan928

You reason that 8.1 takes supported LV 2014, but LV2014 it is not FULLY supported (as in the modules and drivers) FPGA being one of them. The tools of compiler we are dependent on the Xillinx for unfortunately are not at the moment. Although some FPGA compilation may work, not all compilations of go. Unfortunately there is no timetable in terms of how Xillinx & NOR will be fully supported for specific modules with 8.0 & 8.1 window.

Please see the document below to see a complete list of tools or beween compatabilities & 8.0 which can provide assistance

http://www.NI.com/white-paper/14281/en/

Concerning

J

-

Protocol settings NODES in LabVIEW using NI USB-8473

Hi, I was recently introduced to this Protocol for diagnostics on the ECU.

What I want to do: -.

I want to read messages from the ECU using the program called 'UDS Diagnostic Demo', which is available in the game for example provided under the help section in LabVIEW.

I know: -.

I can communicate with ECU very well with the screws of NI-CAN and the same material (8473 NIUSB) I used initially for monitoring CAN messages.

What I want to know: -.

- I don't know about the parameters I put the Protocol Settings section if I use UDS Protocol?

- What are Transmit and receive IDs, are these specific ECU or a few standard values?

- For UDS and ISO TP Normal mode chosen - I learned I didn't need to worry about the ID of the channel and Transmit / receive address Extensions but don't I care about periodical CAN ID?

Also by reading this forum I came across an issue where it was mentioned as a transmit and receive ID 7E8 and 7E0 respectively. I also tried but no luck.

Using values as specified in the screenshot, I'm able to run the VI and it doesn't give any errors but he don't give me any respinses ECU is.

Any help will be much appreciated.

Thank you

Vicky

Hi Frank,.

I'm back with the solution. I managed reading ECU information such as part number, serial number and other settings engine such as temperature, pressure, battery voltage and so forth and on.

When you use the example LabVIEW VIs for the UDS protocol you have no need of the fields under Protocol for diagnostic.vi settings open except transmission and reception ID. (Normal - value ISP TP transport protocol)

After further reading on different ECU. I discovered this ID to pass - 7E0 and receipt ID - 7E8 are aone of the most common ID to connect with most calculators of major manufacturers such as Delphi.

What ID service you will find standard IDs based on Protocol NODES here. For the propreitery ID, you need help from manufacturer or Integrator.

http://www.neweagle.NET/support/wiki/index.php?title=Unified_Diagnostic_Services

Let me know if you have any questions.

Thank you

Vicky

Maybe you are looking for

-

How to prevent the deletion of text Word when drag / drop of Firefox?

When I'm dragging text from a Word document in Firefox, the text is always removed from the Word document! When I do the same process with Chrome, Chrome will leave the text intact in the original document. How can I get Firefox to do the same thing?

-

All my drop-down menus are distorted by the change, the menus and menus on my browser websites. The distortion is so bad that I can't read the menu or choose a selection from the menu without moving my cursor around and sometimes not even then. The m

-

Equium A200-15I - cannot connect to networks

I have an Equium A200-15I and unable to connect to wireless networks. I can connect properly to my network wireless at home and in the past have had no problem connecting to networks wireless in other places. However, recently I have been unable to c

-

HI - another beginner question: Following the tutorial, I created a graph. The graph has a small box to the right to go a legend for the different plots. (I would like to put a picture, but looks like that I do not have permission to do so). The purp

-

Opening a file wave without having to save it first?

I can open & view PPS files & save them then if I want to. I was also able to do this with wave files, but I must have turned off something, because now I have to first download it to a folder, & then open it from there, where before I could click &