LabVIEW FPGA SP1 2012 & EVS1464RT FPGA IO

Hello

There seems to be problems with the new Labview FPGA 2012 SP1 in combination with an EVS1464RT embedded Vision system, which took place only after upgrading to SP1 2012 Labview:

- While trying to compile our code for the EVS1464RT FPGA or (Vision system embedded with e/s based on a FPGA Virtex-II FPGA) Xilinx tools (V10.1, since it's a Virtex-II FPGA) has reported an error saying that the compilation work has tried to set the property 'Data (output events)', which does not exist, so the Xilinx tools just quit with an error.

A complete uninstall and reinstall 'clean' do not solve the problem.

Research has shown that there is a property correct for Xilinx tools, called "done (output events)." An extended search in the Labview upwards 'incorrect data (output events)' some text files in 2 files "resource.xml" in the directories '...\National Instruments\LabVIEW 2012\Targets\NI\FPGA\IMAQIO\IMAQIO-1 "and '...\National Instruments\LabVIEW 2012\Targets\NI\FPGA\IMAQIO\IMAQIO-5' (and nowhere else).". " Change these 2 texts to 'Done (output events)' corrected the error and allowed to compile the code again.

- Another problem is that you can not start the VI FPGA-interactive (for example by clicking the Run button). This product just another error message saying that the VI '...\National Instruments\LabVIEW 2012\vi.lib\FPGAPlugInAG\IMAQIO-5\niFpgaOpenAndRun_IMAQIO-5.vi' could not be found (and there really is not anywhere on the hard drive).

The FPGA VI can be started from an another VI on the target host by using the function "Reference open FPGA". Then it works without any problems, so the bitfile has been obviously compiled correctly.

All of this worked out of the box without any problems on my old installation of Labview (before 2012 SP1 update).

The first problems now seems to be a simple typo, and using the function "Open FPGA reference" is a workaround for the second problem. But I'm very angry that National Instruments does not seem to test their software before releasing. A service pack should never break things that worked before.

Find these alternatives cost me 3 days, which, in my opinion, could be acceptable for open-source software, but not if you pay hundreds of euros per year for a "Standard Service program. For that kind of money, I expected NOT to test all the changes that they do well.

Best regards

Dr. Merlin Welker

Hello Mr. Welker.

First of all, thank you for your comments. I'm really sorry that you stumbled on this issue. Please let me give you some background information on it.

You are right that the update for the versions of service pack is to address reported problems and he should never break things that worked before. Unforunately, a change in LabVIEW FPGA exposed an underlying issue with e/s NOR-IMAQ driver FPGA compilation. We have identified this issue and addressed it in the Acquisition of Vision Software communicated in February 2013, including e/s NOR-IMAQ 2.6.1.

It is now available in the Update Service of NOR. We also found and addressed the issue with the FPGA Open running and run interactively in the thatsame release.

We recommend the upgrade to use the latest version of driver, whenever you upgrade from versions of LabVIEW, to ensure better compatibility between them. Please note that whenever you upgrade LabVIEW FPGA or Vision Acquisition Software, you should also recompile your LabVIEW FPGA projects.

While these issues were found and corrected in the latest version, we are now reminded our development and testing processes for future versions. Please accept our apologies for the inconvenience. National Instruments is committed to your satisfaction and to maintain your confidence in our products.

Thank you

Elmar

Tags: NI Software

Similar Questions

-

Hello

I'm trying to interface labview fpga to 2012 with Spartan E 500

I am facing two problem

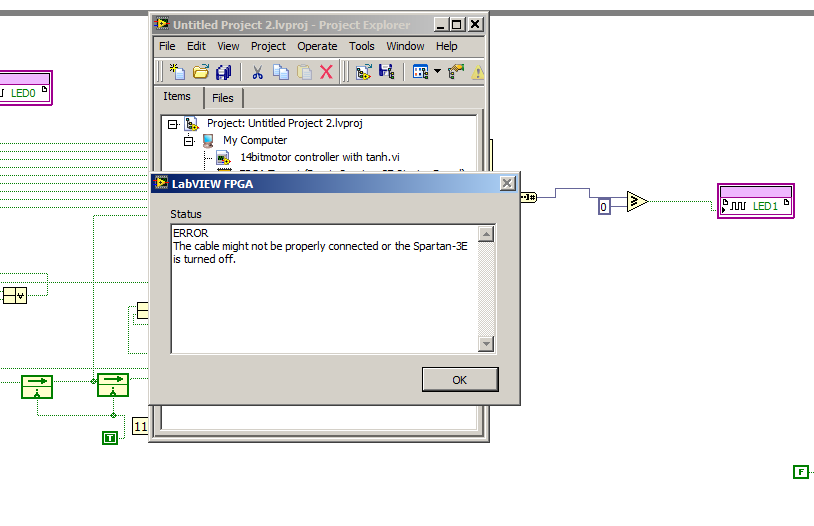

a first in the figure below when I try to download Flash memory of Spartan E?

I run vi on Spartan works well but when I download it the error appear

also there is no "" "run when loading" "button which are available in a previous version of labview.

Please help

I don't have a LVFPGA version with the support of 3rd Spartan installed in front of me, so I'm working from memory here, but the option to run the VI on charge moved to the target property page (available on a right click on the target'Properties) of the standard build for the VI (as shown in your own message here)

-

LabVIEW FPGA: An internal software error in the LabVIEW FPGA Module has Unknown

Sir/Madam,

Note Labview 2012 SP1 installed about 2 weeks ago.,.

Accident occurred during the compilation of an fpga vi who worked satisfactorally in the past.

When I restarted and went to the message recomplile "LabVIEW FPGA: an internal software error in the LabVIEW FPGA Module" see attached picture of popup.

I reinstalled Labview in its entirety and backed out the changes I made to the vi but still get the same message.

Thanks in advance

Daryl

It turns out that the question was in the VI and not of LabView FPGA module as the message may indicate. I created a vacuum vi, cut and pasted items in this from the vi error and recompiled and it ran very well.

Somehow the vi has been corrupted internally.

Thank you it's fixed.

-

Error when create control LabVIEW FPGA CompactRIO

I have error when you try to create a new model of LabVIEW FPGA CompactRIO control project. I tried with LabVIEW 2014 and 2014 SP1 update. This error always occurs.

Please help me with this.

Kind regards

Thang Nguyen

Hello

I fix the problem by removing LabVIEW 2014 SP1 and reinstall again. After the reinstallation of LabVIEW, I create the project template.

Kind regards

-

LabVIEW FPGA: Problem compiling look-up Table

Current versions of software:

LabVIEW 2014 SP1

LabVIEW FPGA 2014

Xilinx Vivado

I'm having a huge problem in trying to compile my LabVIEW FPGA code.

Some recall of the code:

It's all in a SCTL.

I am streaming in a FIFO DMA and comparing it with the values previously stored in the shift registers (which are initialized to 0 at the start of the loop) in the SCTL.

The results of the comparison are then piled into a U16 and loaded into a lookup table (I use the LUT - 1 d), and I'm so help this LUT to decide what value will be charged to travel to record for the next iteration of the loop, which, in any case, would be either the current values of the flow, or the post previous registry value.

(It's a triage loop)

I am able to run very well in simulation mode code, but when I try to compile, I get this error:

"The selected object has a built-in shift register that makes the output on a particular loop iteration correspond to the entries in the previous iteration."

Connect the outputs of the object directly to a minimum number of nodes of Feedback or uninitialized shift registers. You cannot connect the outputs to another object.

See using LabVIEW for more information on the objects with registers embedded offset. »

Someone at - it ideas why this happens, and what might be the possible solutions?

I'm tempted to break it down into separate loops, but I prefer not to because it is now a loop (and working in my simulation).

I found my problem.

Any time that a LUT is in a chain shift register, it cannot:

1. be part of a string of shift register that has a variable initialized

2. follow-up to no decisive structure, like a box structure.

I just moved the position of LUT and it works.

-

HELP - FPGA SPARTAN 3E-100 CP132 WORKS WITH LABVIEW FPGA?

HI EVERYONE, GET ON IM TRYING TO USE MY FPGA WITH LABVIEW, BUT I DO KNOW THAT IF ITS COMPATIBLE, I INSTALLED THE DRIVERS, MODULE FPGA AND LABVIEW 2012, IM USING WINDOWS 7 32 BIT, AND AFTER I COMPILED ITS SAYS:

LabVIEW FPGA called another software component, and the component returned the following error:

Error code:-310601

NOR-COBS: Impossible to detect the communication cable.

Check the communication cable is plugged into your computer and your target. Also, verify that the proper drivers are installed.Thank you.

=)

Hi dvaldez2.

LabVIEW FPGA offers no support for any material to third parties, other than the 3rd Spartan XUP Starter Kit. These are probably the drivers you downloaded.

http://digital.NI.com/express.nsf/bycode/Spartan3E?OpenDocument&lang=en&node=seminar_US

However, this driver supports only the Starter Kit Board itself (http://www.digilentinc.com/Products/Detail.cfm?NavPath=2, 400, 790 & Prod = S3EBOARD). You may not use the driver with any other Xilinx FPGAS.

I hope this helps.

-

Version of the C API for LabVIEW FPGA 2011

What is the version of the C API that will work with LabVIEW FPGA 2011?

I guess as this one: http://www.ni.com/download/fpga-interface-c-api-2.0/2616/en/

Version numbers seem to start by 2012 years. It's the latest version I could find before 2012 and he was released in August 2011. This time coincides with the annual festivities of the NOR week where a large part of the software/hardware is released. It's a small download, so it shouldn't be difficult to download it and try it.

But, you'll still need LabVIEW FPGA development according to this white paper: http://www.ni.com/white-paper/9036/en/

-

Simulate the sine wave using LabVIEW FPGA with NOR-myRIO and display in real time

Hello

I'm relatively new to LabVIEW FPGA. I am trying to test (and later apply) controllers high speed on myRIO.

At this point, I'm trying to simulate the sine wave from 1 to 10 kHz using Sinewave generator VI express. I also intend to display the sine wave on the time real (RT) using FIFO. However, I had a bit of trouble to understaing various synchronization parameters.

1. how to encode information about the sampling frequency generating sine wave? (The side FPGA vi requires only the frequency of the signal and possibly phase and does not rate update lines)

2. how to estimate the number of items in a FIFO? (that is, the relationship between the rate of updates to loop (RT), the signal frequency, sampling frequency and the number of items in the FIFO)

It would be great if we could share a very simple program (side host and target) that did something similar.

Thank you

MILIN

Milot,

I think the problem is the type of data in your FIFO. Your FIFO is configured to use a data type of I16. The problem is the number, it displays only ever will be-1, 0 or 1. To resolve this problem, you must send the sine wave as a fixed point data and convert it to a double on the side of the RT. This should significantly improve your resolution.

-

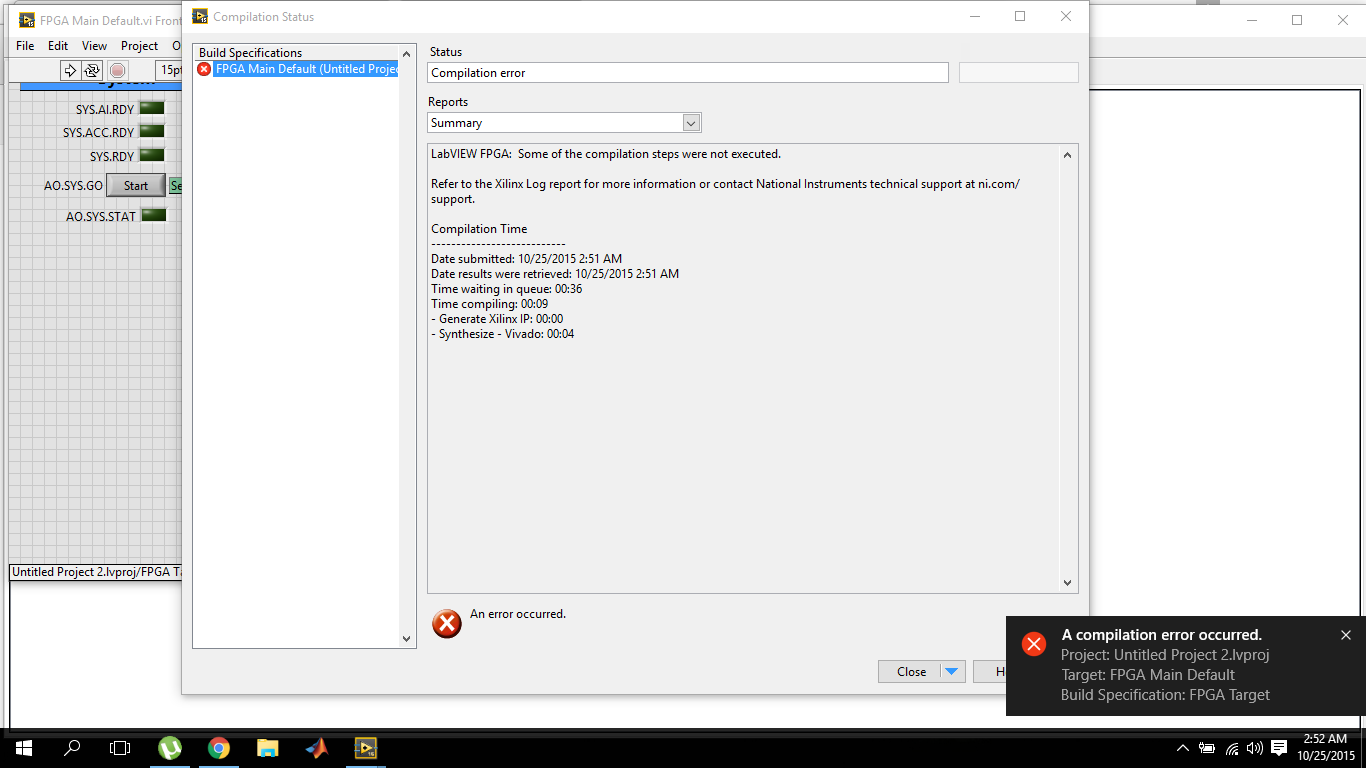

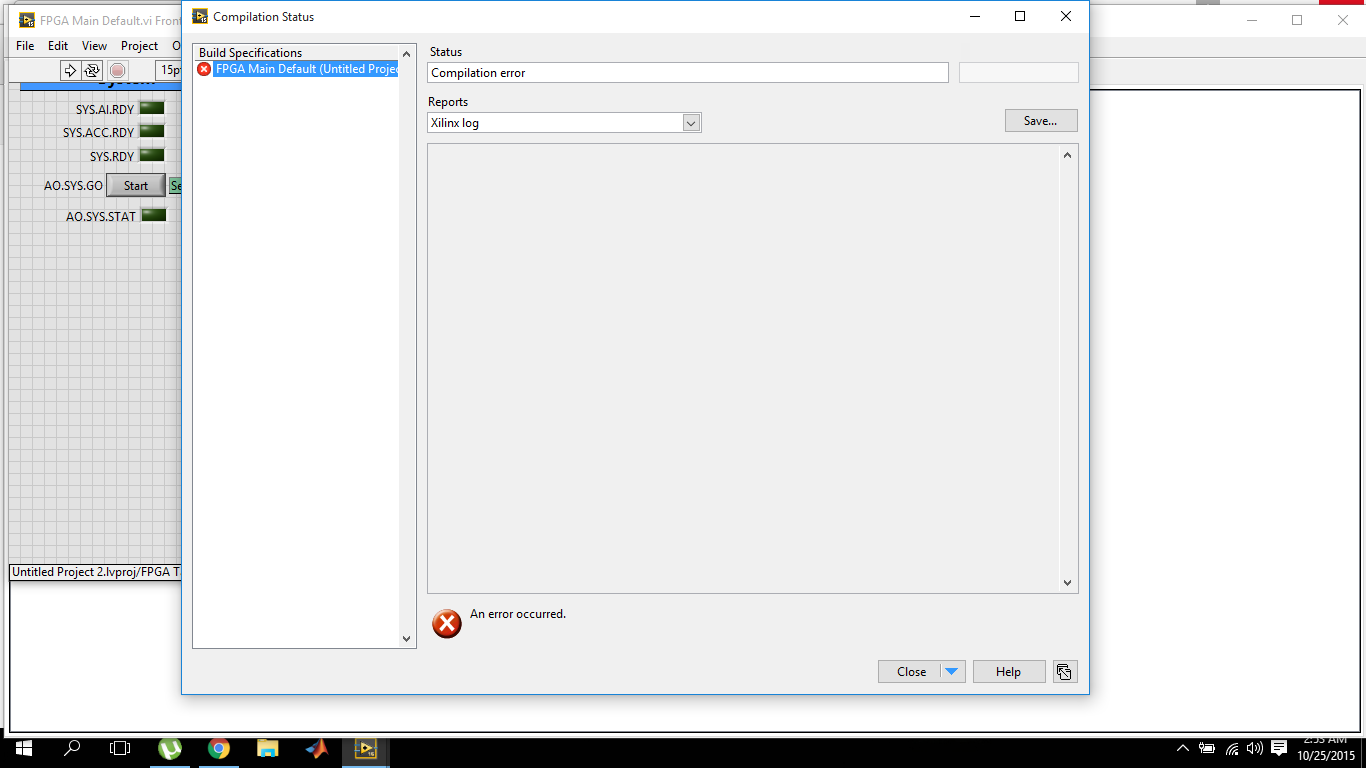

LabVIEW FPGA, 2015 compilation error

I've recently switched to LabVIEW 2015 and I'm working on OR myRIO. So also installed myRIO 2015 bundled software. The problem I have is that the compilation of fpga fails within 10 seconds.

and the target Xilinx journal report is empty

The first time when I tried to compile on 2015 version, it failed and the message box that failed came alongwith the avast antivirus warning for malicious activity. I reported it as wrong and now I tried several times with avast shield disabled control, but the results are the same. While the version of labVIEW 2014 works very well.

Now, I'm sure that there is something wrong with the installation of Vivado because this dll is part of it. The dll must be default in the2014_4\lib\win32.o directory C:\NIFPGA\programs\Vivado if you are using an operating system for 32-bit AND also in C:\NIFPGA\programs\Vivado2014_4\lib\win64.o If you use a 64-bit operating system. If the dll is not here, it is probably that the anti virus (I've never seen what happens to Xilinx but I have for other stuff).

I'm emphasizing the 2014_4 because LabVIEW 2015 uses Vivado 2014_4 while 2014 LabVIEW uses Vivado 2013_4. Since you have also installed LabVIEW 2014, you must have 2013_4 as well and if it works, you will find the dll I just wanted you make sure you check the correct directory for the Vivado 2014_4.

Download and install (reinstall or repair if already installed) 2015 LabVIEW FPGA Module Xilinx tools Vivado 2014.4. You can also use the DVD Setup if you have. It would be a good idea to do the installation with the disabled and even anti-virus try the first compilation the same. Try and let me know if the problem persists.

Kind regards

-

Internal software error of LabVIEW FPGA Module - 61499

I get the error next (in a pop-up window) in the phase of sompilation for the FPGA target with a vhdl IP. This error continues to occur even after restart LabVIEW and the PC. Someone at - it solved is this kind of problem before without having to re - install the software?

Here is the error information:

Error-61499 occurred at niFpgaXml_GetValue_String.vi<><><><>

Possible reasons:

LabVIEW FPGA: An internal software error in the LabVIEW FPGA Module has occurred. Please contact National Instruments technical support on ni.com/support.

Additional information: lack the tag required XML (/ CompileServerList)

As a first step, I can compile the vhdl IP node successfully. However, once when I'm running a VI with the FPGA, the bureau stop working. After that I restarted by force, it cannot perform the build of a vhdl IP node. Even without connecing to the jury of LabView, he pointed out errors before the end of the sompilation.

Interestingly, the screw which also includes nodes IP vhdl that I properly compiled before, I can still run the VI to the Commission and it works correctly.

Thank you

Looks like your ActiveJobsList somehow has been corrupted. I saw occur when computers are hard stop or blue screen during compilation. I don't have that LabVIEW 2014 installed on my machine, so your path will be a little different, and the file extension will be a .txt or .xml instead of .json, but try this:

Move the file "C:\Program Files (x 86) \National Instruments\LabVIEW 2014\vi.lib\rvi\CDR\niFpgaActiveJobList.json" (or your equivalent) out of the above directory (back it upward and delete essentially) and restart LabVIEW. Must regenerate the file and resolve the problem.

-

How to use bidirectional I/O in the CLIP of LabVIEW FPGA?

How to use or define two-way i/o for CLIP with LabVIEW FPGA? I want to use 1-wire communication inside the kernel CLIP, the function will be implemented to read and write as I/O inside the CLAMP.

The XML Generator (CXG) 1.1.0 ELEMENT does not support.

Thank you

Supawat

Work after separate IB pin (bidirectional) at the entrance and exit. Thank you.

-

NEITHER 9512 with Labview FPGA Interface

Is it possible to use the NI 9512 stepper with Labview FPGA interface drive unit or is it only possible to use it with the interface of scanning? When I try to add the module to a FPGA target, I get an error telling me that Labview FPGA does not support this module with the latest version of NOR-RIO, but I have the latest version of OR-installed RIO.

Hi Checkit,

You're right - the 9512 cannot currently be used in FPGA. There is an error in the documentation. The 9514 and 9516 can, however.

-

How to measure the frequency of sampling (s/s) in LabView FPGA?

Hello

I am trying to find a way to measure the sampling frequency (s/s) during which I read from analog input in LabVIEW FPGA. I know that the sampling frequency is specified in the data sheet of the module HAVE, but I want to measure in LabVIEW.

Any suggestions?

A screenshot of the example code would be greatly appreciated

Hey phg,.

If you have some time loopand in this loop, you export a sample by iteration of loop via an I/O node. You can't out two samples on the same I/O node within an iteration, it's always one!

So if your loop takes 1 second to run you have a sampling rate of 1 Hz output. The same goes for sampling of entry. How long your loop takes to run can be calculated as explained above.

Samplerate [s / s] = 1 / [s] while loop

-

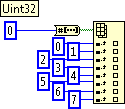

Int split into pieces in LabVIEW FPGA

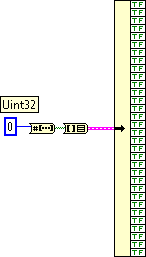

Is there a clever way to split a Uint32 in 32 bit directly accessible (not a prison guard) in LabVIEW FPGA?

The only way I could come up with is the following, which is a writing of pain for 32 bit and seems a waste resources og to store all these clues.

.

Best regards, mola

I thought about it. I could use clusters by right-clicking on the table to the Cluster block and increase the cluster size in 32.

-

LabVIEW FPGA: Integration node clock wrong

Hello

I'm having some difficulties to understand how the clock is part of the node IP for LabVIEW FPGA and was hoping to get some advice.

What I try to do is to set up a digital logic circuit with a MUX feeding a parallel 8-bit shift register. I created the schema for this Xilinx ISE 12.4, put in place and can't seem to import the HDL code into an intellectual property node. When I run the VI, I am able to choose between the two entries for the MUX, load the output in the shift register, clearly the shift register and activate the CE.

My problem is that when I switch to the entrance of THIS, he should start 1 sec shift (Boolean true, SCR, High, what-have-you) in the registry once each clock period. Unfortunately, it instantly makes all 8 bits 1 s. I suspect it's a question of clock and here are some of the things I've tried:

-Specify the input clock while going through the process of configuring IP nodes.

-Adding an FPGA clock Constant as the timed loop.

-Remove the timed loop and just specifying the clock input (I'm not able to run the VI that I get an error that calls for a timed loop)

-Do not specify the clock to enter the Configuration of the IP node and wiring of the FPGA clock Constant to the clock input (I can't because the entry is generated as a Boolean).

-Remove an earlier version of the EC who had two entries up to a door and at ISE.

-Specify the CE in the process Configuration of the IP nodes.

-Not specify this in the process of setting up nodes IP and wiring it sperately.

-Various reconfigurations of the same thing that I don't remember.

I think I'm doing something wrong with the clock, and that's the problem I have. Previously, when I asked questions to the Board of Directors on the importation of ISE code in LabVIEW FPGA, a clock signal is not necessary and they advised me to just use a timed loop. Now, I need to use it but am unable to find an explanation online, as it is a node of intellectual property.

Any advice would be greatly appreciated, I'm working on a project that will require an understanding how to operate clocks the crux of intellectual property.

Thanks in advance,

Yusif Nurizade

P.S. I have attached my schematic ISE and the LabVIEW project with one of the incarnations of the VI. The site allow me to add as an attachment .vhd file, but if it would help I could just paste the body of the code VDHL so just let me know.

Hello Françoise,.

I spoke to the engineer OR this topic and it seems that it was sufficient to verify that your code works, by putting a wait function of 500 ms on the while loop to check that the registers responsible and clear. I'm glad that it worked very well!

Maybe you are looking for

-

Need driver Win7 for my Satellite A300 webcam

Hello, I am looking for the drivers on my webcam.My model is Toshiba Satellite A300. In the official page, it has drivers for the webcam in windows 7. Thank you

-

How to skip the Startup Repair...

How to skip the Startup Repair... I started from the install disc and want to "restore full backup for PC. I selected the partition with the corrupt windows installation. The process is suspended, check disk for errors. This check can be ignored. I k

-

Extract data from budget of Ebs use native adapter in FDMEE

Hi team,Please tell us how can I get budget data of Ebs with native adapter. Is it possible, as we can learn real separately and budget separately and categorize. Also it stating that we are pulling real from table GL balances. Please advise has frie

-

What is the problem? Perhaps Java version? IE version?Someone there troubleshooting tips?I'm not a ColdFusion programmer, but am pretty tech savvy.Any help is greatly appreciated.

-

Computer laptop HP G62 does not load

I have a hp G62 154-canotebook. About 6 months ago, there was a problem with the cooling system (nothing to do with the fan a kind of plate), but fortunately it has been supported by my warranty with hp. Three months after my battery problem has sta