Question of FPGA on speed

I have as part of the much bigger problem simply multiply the elements of the two tables and summarize the terms to give a single output constant.

There may be 100 terms mean in the table, but this test that I attach only uses 6 numbers and the same table twice for simplicity. I'm so calculate the scalar product of two vectors of surface where ' is transposed.

It has been suggested that I shared the calculation in two so that I have summarized the first 3, i.e. 0,1,2 and 3 last, IE the 3,4,5 in parallel (as in the program). Of course, I get the same end result. Would this double FPGA execution speed because it's doen in parallel?

The reason why I ask this question which is probably if I used a power of 2 amount of data I could divide it again and still a bit like a FFT,.

Does make sense? or is the FPGA "unpack" the loop FOR in any case is not worth?

the program displays the original and the split method.

Thank you

The side is an FPGA will give you gains of speed whenever you parallelize computation. The downside is that you still have to do most of it. No shipping FPGA course OR product made optimizations such as loop place (although the standard LabVIEW). This is a dangerous operation that could increase the size of the code and FPGA programmers tend to be picky about these things.

If you can get speed gains each time you parallelize, but you will have to do it manually. Note If your parallel loops that access a shared resource (memory, state variables, etc.), the claim on this resource will reduce the overall speed, so you get. Also, if you can integrate calculations in a single-cycle timed loop, you will get there, effectiveness as well.

Good luck and have fun!

Tags: NI Software

Similar Questions

-

Understanding on the 9505 FPGA VI speed control

I was able to quickly use the 9505 Servo Drive example for closed loop control of position on the FPGA, but I can't find how to change the code to take in charge the speed control (which I need to another axis). I'm doing my changes on the FPGA VI itself rather than on the side of RT Softmotion.

Here are the questions I have:

If I use the PI speed loop with my speed and a set arbitrary control speed, I see the speed stabilizes (engine power seems uniform), but I can't correlate with the other speed reference that a larger number is faster. Speed (from the loop of the encoder) seems collating in values from 0 to 2 just on my FPGA VI (I do not understand the units, but I see my position change on my collation of encoder in thousands of pulses per second). Why are they so different/how I have adapted my encoder speed correctly?

Using just the delivery example 9505 Servo Drive (position control), how to set the speed of moving of the FPGA code (in interactive mode)?

Hello

Speed is defined through position set points. Control of the speed in the screw RT does not actually send speed commands to the reader, but sends position set points at a known rate. Given that the position set points are sent at a constant rate, an effective speed can be calculated.

A method to do so via the FPGA would synchronize a loop in your FPGA code for the analytical engine, which has a known rate. Once this is done, you can calculate the actual speed of the engine.

-Erik S

-

HY all!

I have a few questions using Xilinx compiler tools.

The reason why I want to use FPGA is to get the analog measurements of two modules NI 9205 and also filter these measures. Modules are configured to run in terminal diff mode, while the other parameters of this module are set to default values (+/-10 V etc.).

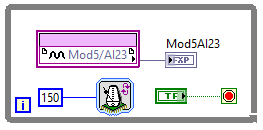

2.1 when I try to compile the program easier - read one analog measurement every 150 US, see the figure below - just compilation takes too much time, namely fear for a few hours, specifically, compiling stucks on mapping. I followed my PC performance, processor is about 20% 3.84 GHz, while the memory is on 10% 31.9 GB. Q1: is it possible to configure the compiler to use as many resources as possible PC?

I'll post probably questions once I managed to get this simpler program to work

Thank you in advance!

Best regards

Marko.

Hello

What operating system do you use? I read somewhere on this forum that windows 8 and possibly windows 10 are not taken in charge by xilinx compilator.

I have simular problem faceing with the compilation of the code. On Windows 8 compilation take over 50 minutes and not finished yet. Then tried to compile the same code on Windows 7 it only take 10 minutes. -

General questions about FPGA Interface C API 2.0

I developed an application in LabVIEW FPGA 2011 on a Board of the R-Series PXI and a host application LabVIEW 2011 Windows XP to communicate with him via DMA FIFO. I'm trying to adapt the interface to CVI 8.1 (preferred) or CVI 2009 using the Interface of FPGA C API 2.0. The example of FIFO that it stores in the directory C:\Documents and Settings\All Users\Documents\National Instruments\FPGA Interface C API\Examples\ gave me a few questions:

- The functions NiFpga_WriteFifoI16 and NiFpga_AcquireFifoWriteElementsI16 are two different ways to do the same thing? I wasn't clear where I do the extra copy if you use NiFpga_WriteFifoI16. I guess the combination of NiFpga_AcquireFifoWriteElementsI16 with NiFpga_ReleaseFifoElements is the way to go if I want to stay out of trouble.

- I intend to call NiFpga_Initialize and NiFpga_Open in an initialization function that gives the word initially, then keep the session handle in calls to other functions. The session handle is always not null when it opens successfully? Could I use it as a test to make sure that I have a session valid before calling any other functions-example:

If (session) {NiFpga_WriteFifoI16 (...)} - Interface of FPGA C API 2.0 is only announced work in CVI 2009 up on. If I include NiFpga.c and .h in my project CVI 8.1, it seems to compile fine, but I did have the chance to integrate yet. Is there something specific that would make CVI 8.1 not work? Our deployment environment of difficult application CVI upgrades

-Jim

Jim,

With regard to your questions:

1. Yes, these two functions are the same, however there is a big difference between the two. NiFpga_AcquireFifoWriteElementsI16 acquires, prepares and publishes FIFO elements to avoid the need to write the first in a buffer allocated by the separate user, then copy the contents of the elements in the memeory host buffer. Considering that, in the NiFpga_WriteFifoI16 does not work. So the NiFpga_ReleaseFifoElements should always be used with the NiFpga_WriteFifoI16. The example is just showing how the code should be used, but is not necessarily displayed works should be used together. I understand perfectly why he was confusing.

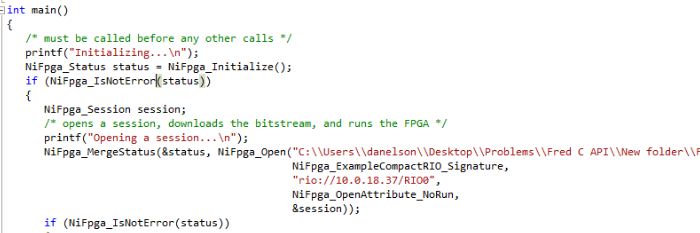

2. the best way to ensure you have a valid session is by using the NiFpga_IsNotError() function. I've attached a screenshot of the example code that illustrates how best to achieve this and inserted the image below.

3 regarding using CVI 8.1, there is nothing in particular, which would make your code does not work in point 8.1, but we can guarantee that C API 2.0 will work correctly with 9.0.

Kind regards

Larry H.

-

Satellite L50 - A - 1 5 - question about max LAN speed

Qualcomm-Atheros AR8171/8175 PCI - E Gigabit Ethernet Controller (NDIS 6.30)

In the specifications it is said that this network adapter might work on the speed of the LAN 1 Gbps 1000base-t.

But the max speed that is displayed on my system is 10BASE-T/100BASE-TX.

Why?System: _

Toshiba Satellite L50 - A - 1-5

Windows OS 8.1

Driver version 2.1.0.21

Qualcomm-Atheros AR8171/8175 PCI - E Gigabit Ethernet Controller (NDIS 6.30)You're right, the network adapter. Atheros QCA8171B supports networks: 1000BASE-T/100Base-TX/10Base-T

To use the range, the router should also support the 1000BASE-T.

Did you check that?In addition, you can change the LAN settings in:

Device Manager-> LAN card-> properties-> Advanced tabHere, you should check if 1000BASE-T option is selected and chosen.

I also recommend you check the BIOS settings because as fat I know some LAN function can be enable/disable in the BIOS

-

Question of FPGA compile farm 2012

I was under the impression that my FPGA LV code can be compiled by several workers when I bought and installed the FPGA compile farm Toolkit. What I have, however, is that each work of compilation can only be compiled by a worker. I expect that a single compilation work can be divided by the number of workers.

So I see that a worker of computers will compile two computers of worker work. It's just that a worker will be compiled at the same time.

I just misunderstand the features to compile farm Toolkit or is it an installation problem?

Thank you

No, a unique compilation cannot be shared between workers. Nature of the beast-FPGA "compilation" is not something that lends itself to parallelism. You have the advantage that the build tools run much faster under linux, however.

-

Quick questions of FPGA: Broadband Division vs Multiplication implementation (rounded)?

Hi all

I'm trying to implement a simple routine where I divide a FXP by number 7 to the FPGA. I wanted to use the broadband division, but it seems only to round to the nearest integer even if the output is capable of representing fractions. Otherwise, I can multiply my number by 1/7 using the proliferation of broadband and I get what I want. I'm not too familiar with arithmetic FXP. At least without understanding the problem, I have a solution that is to use the multiplication. I just want to know a little more. Can someone please shine an idea on why the division rounds even if he can manipulate fractions?

Thanks for your help

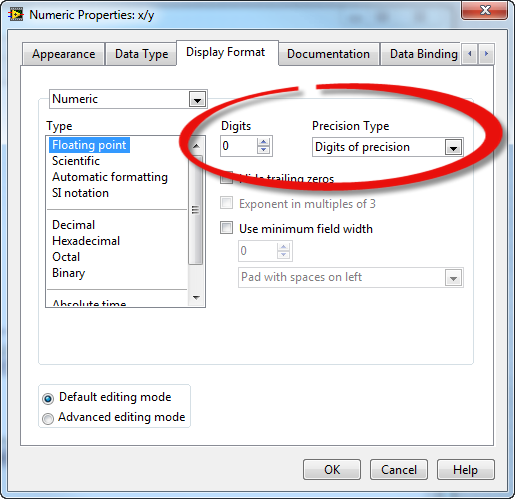

Somehow your obtained initial indicator set 0-digit precision for display formatting. This means that the data are indeed correct and there, but the text format of the on-screen display rounded to the whole number.

Any ideas how this parameter has changed?

-

question pxi_trig FPGA with multiple cards

I'm trying to get several cards to control and drive the same pxi_trig line. The goal is to have all the cards to follow the same trigger line. When a card is said to occur, other cards should detect it. I found a similar problem discussed here, http://forums.ni.com/t5/PXI/pxi-trig-problem/m-p/1013201, but I try to avoid having a master / slave relationship. Again I want any card capable of steering the trigger. If I understand that the problem has been resolved with the method "Set exit help", I don't see the expected behavior.

Any help would be greatly appreciated.

Hi Thatguy,

It seems that what you're doing should work. As long as you reference the same trigger, they will all use the same physical wire from the PXI backplane.

I don't follow the logic of sense, though, but I guess what you're trying to do is to determine if this card tries to lead the line, while the value"Set out".

One thing to note when the line is not used, it is drawn up. I don't know if this could be what you see or not.

What behavior do you see?

Dave T.

-

Question of FPGA (INCREASE of Cast)...

-

Questions of size and speed of Collection stored

Hello everyone,

Developing a search engine for text, I was looking for a quick tool and low level storage. Berkeley DB I got and it seemed to suit my needs. I used Java cards to my process if it appeared logical to use the Collections API.

Structure database (or card):

DOCUMENT MAP

- docKey a simple integer ID generated in the order

- docEntry small number of properties

TERMMAP

- termKey, a unique string value

- termEntry small number of properties

INDEXMAP

- indexKey two foreign key values: docKey, termKey

-number of occurrence indexEntry of this term in the doc

There is a secondary index for INDEXMAP termKey interrogation.

I use the tuples of the key entities serializable for entries and I removed the redundant entities serializable key value using the transient modifier.

Here's the algorithm

The program retrieves the terms of a document and add the doc in the DOCUMENT Explorer.

For each term, if it is not in the TERMMAP, it is inserted.

This isn't in the INDEXMAP, it is inserted and the number of occurrence = 1 if the number of occurrence is triggered.

DOCUMENT map is quite small, while TERMMAP and INDEXMAP in particular have a huge amount of entries.

When testing it, it has very well worked and provided a quick mark. However, I noticed a few problems that could be critical:

-The size of the log is very high

1, 5 GB size of total newspaper for 100 MB of text indexing, then the same index (without the secondary index) takes 100 MB in ASCII text.

I tried to reduce the total log by increasing CLEANER_MIN_UTILIZATION but it has not reduced sufficiently.

I thought that maybe does not keep good things, but by displaying the contents of the card, all goes well, no redundancy.

-The storage is too slow

With a simple file storage, it's very fast if the bottleneck comes from db storage.

I noticed that it is faster to store temporary data in java cards (TreeMap to have sorted input values), then add them to the maps stored than to use the saved directly map.

To conclude

My final goal is to process a huge amount of data (collections of giga or terabyte) and I'll probably have to use parallel processing. However, if a simple test gives good results, I fear that I'll have to find another way to store my data.

This is the first time that I use berkeley db, so maybe I did something wrong. To avoid asking help for nothing I tried a lot of changes in the configuration: size, cleaner use, size of the cache, off transactional stuff and nothing gave significant results. I followed the tutorial for Java Collections and read the Javadoc. Finally, I used the JConsole plugin to take a look at the stats. This is my last chance...

If more details are needed, just ask,

Thank you in advance,

Nicolas.

-

Very basic question about how to speed script CLEARDATA.

CLEARDATA:

========

Hi there, the two scripts will cause the same, but the following, which is faster (1) or (2)? Assuming that the data and the same sets for each. Thank you!

CACHE ALL TOGETHER;

SET CACHE HIGH;

SET AGGMISSG

SET HIGH LOCKBLOCK;

SET CALCPARALLEL 4;

UPDATECALC OFF SET;

(1)

DIFFICULTY (& InitPeriod: & ActualPeriod, & ActualYear, & CalcScenario, "WorkingInput")

@IDESCENDANTS ("business district"), @IDESCENDANTS ("CC"), Fix (@IDESCENDANTS ("Entity"), @IDESCENDANTS ("Product")) <-sparse Dimensions

CLEARDATA "USD";

ENDFIX

ENDFIX

CLEARBLOCK VACUUM;

(2)

DIFFICULTY (& InitPeriod: & ActualPeriod, & ActualYear, & CalcScenario, "WorkingInput")

CLEARDATA "USD";

ENDFIX

CLEARBLOCK VACUUM;CACHE ALL TOGETHER;

SET CACHE HIGH;

SET AGGMISSG

SET HIGH LOCKBLOCK;

SET CALCPARALLEL 4;

UPDATECALC OFF SET;DIFFICULTY (& InitPeriod: & ActualPeriod, & ActualYear, & CalcScenario, "WorkingInput")

DIFFICULTY (@RELATIVE ('entity', 0), @RELATIVE ("Business Area", 0), @RELATIVE ('CC', 0), @RELATIVE ("product", 0))

CLEARDATA "USD";

ENDFIX

ENDFIX

CLEARBLOCK VACUUM;Fixing Level0 blocks like the above calc data erasure

Loading new data

Setting the update rollup on Aggmissing

The Total process takes less time compared to

Deleting the data for all levels

Loading new data

ROLLUP -

High speed FPGA for MyRIO personality

Hello

I started on My Rio 1900 who I am trying to program in C language, so without the use of Labview.

I did sample a signal.But I would like it sample at a higher frequency that it is possible with the default standard FPGA personality.

I downloaded it on ni.com, but installation requires Labview 2014...So my questions are:

How can I do to work with the personality of FPGA high-speed in c and how do I install it without Labview?Thanks in advance for your help

Best regardsFrançoise

Hello fm16,.

Personality OR broadband to MyRIO without LabVIEW FPGA is not supported, sorry. As you can see:

1) http://zone.ni.com/reference/en-XX/help/373925C-01/myrioreference/myrioref_high_throughput_vis/

2) http://www.ni.com/tutorial/52864/en/

use high-speed FPGA personality VIs to LabVIEW, because the Add-on's code in LabVIEW, so that you cannot use in C.

Best regards

Mariana

-

Speed of memory - Equium A200 PSAF5E

Hi all

I have a Toshiba Satellite A200 - 1V0

Model no. PSAF5E - 001003sp

BIOS version updated to v. 2.50Everest Ultimate 4.5.1330 says I have 2 GB of RAM, two sticks of Samsumg DDR2-667. Also, he also says that my FSB is 133 Mhz with the correct speed of the CPU and multipier.

The problem with the speed of the memory. It shows the capable DDR2-667 sticks and chipset, but DRAM ratio: FSB is set to 8:4 resulting in DDR2-533, in any profile of energy. The system works in configuration dual-channel 128-bit, so I lose 2144 Mbps of transfer speed.

The chipset is identified as a website Intel Crestline-GML GL960, Everest and Toshiba show as claims the site Intel Web capable, DDR2-667 on DDR2-533.

Link: [http://uk.computers.toshiba-europe.com/innovation/jsp/SUPPORTSECTION/discontinuedProductPage.do?service=UK&com.broadvis ion.session.new = Yes & PRODUCT_ID = 138201]

Link: [http://www.intel.com/products/notebook/chipsets/gl960/gl960-overview.htm]

I have found no info motherboard or manual, so here are my questions:

-Is it normal speed or can I expect mode DDR2-667 with this system?

-Is the speed drop memory in dual-channel mode?

-If I re - install the memory modules one by one and change the position could reset the values of the speed of the system?

-Can I access any hidden BIOS settings to tweak the memory? (I have a system of Medion who hid and protected by word accessible via F11 instead of F2 BIOS mode where I can find a lot of options is not not in the normal BIOS F2)

D ' other ideas?Thanks in advance. Any help would be much apreciated.

Hello

The laptop A200 - 1V0 supports the Chipset Mobile Intel® GL960 Express.

Chipset Mobile Intel® GL960 Express tuning a 533 Mhz FSB (front side bus)

http://www.Intel.com/products/Notebook/chipsets/GL960/GL960-overview.htmThe laptop was equipped with DDR2 667 Mhz modules but due to the limitation of the FSB, the modules of memory can only run at 533 Mhz.

All that s

-

Replacement of FVS336v2 due to the lmitation speed

Hello everyone,

We used to have a Netgear FVS336Gv2 that we are more or less satisfied. Combined with 2 times WAN with 16 Mbit/s down and 1 Mbps upstream each she worked enough (small problems here and there and a strange behavior from time to time, but nothing really serious).

Now, we went from a 10 Mbps upstream with an option for an upgrade of the second WAN and WAN to 150Mbps Down - and the problems begin. We will only succeed 25Mbps downstream but complete upstream. A little searching in the forums revealed that others are facing the same problem: 60Mbps LAN-to-WAN throuput according to the datasheet but only about 30Mbps of actual downstream because of the current firmwares. Therefore certainly a replacement. To do this, we received a few questions:

1. the speed of LAN-to-WAN in the technical sheet: is it measured by WAN connection or for the two networks combined? If it's the combined speed even the refreshed hardware version (FVS336Gv3 with 350Mbps) won't be enough for us, when you apply the same relationship between a nominal flow and real LAN-to-WAN. We need at least 300 Mbps of real throughput LAN-to-WAN.

2. in the forums, I found an ad that Netgear will close some of its sectors of activity from 01.01.2017. About the lack of truly new products lately in the VPN Firewall section, we have the fear of buying a product that will be liked in the year.

Does anyone have information on these points? We would be really happy about that.

Best regards

Michael Beaver

Hello okadis,

Welcome to the community!

To answer your questions, the speed of 60Mbps is actually a combination of the two WAN ports even as the FVS336Gv3 with 350Mbps (also combined speed of the two WAN ports). So if you want to use 150 Mbps of download speed, you may need to upgrade to the v3 version. For your second question, it is only for the UTM series and does not apply to VPN Firewall.

I hope that the information I posted has answered your questions, let us know.

Thank you

-

cRIO-9118 FPGA and or cRIO-9022 RT.

Hi all.

Having trouble to get my design FPGA compile for the target.

The error is the overuse of the DSP blocks. 64 available on target...

Do I have to reduce to a minimum the number of blocks of multiplier?

Or can I somehow multiplex on DSP minimixe DSP multivariate use?

Thank you.

FPGA high speed multiplier Math must be set to LUT and not AUTO, because it will use DSP and not LUT car if there is too little of DSP.

This will reduce use DSP, but increase the use of LUT.

Maybe you are looking for

-

Need drivers for Windows 7 for Satellite A100-773

Hello I need Driver Windows 7 for Satellite A100 773 (A) display!(B) sound?(C) WiFI!

-

How to use Boolean as a constant push to add more values

Hello everyone, I am trying to use a Boolean OK button and a constant to do something similar to the calculator project that I read in other posts. I scored $1.00, $0.25, button... So now. I just want to add the value of an indicator whenever I pre

-

Navigation to a controls tabs of a tab control page returned by a server VI call

Hello Purpose a documentation exercise, I wish I could) 1 load a VI by program 2) determine if the tab control is present, if yes how many tablets and if it has a built-in tab control sequence sequence 3) thanks to tabs, snap the front (FP) and the i

-

ACPI\VEN_ASD & DEV_0001 device driver

Hello I need help, download a driver for the device to windows 8 ACPI\VEN_ASD & DEV_0001 I know that I need the sp63687 driver but when I downloaded the file is corrupt. My laptop is a HP Pavilion 13z-p100 CTO x 2 PC Thank you TV

-

CE651F, VNC8V15829, W7 - 64Or spooler, no printer reports error. Printer starts a job and he finished, but not all pages will print. For example: the job is to print pages 45 - it prints 10 or 15 pages and finishes (without error). The work is correc