Fpga PCIe-1473R project

Hi all

I am creating the FPGA code for the card PCIe-1473R. When you try to create a new FPGA project, this card is not among the hardware options that I am able to choose, and no other options have the same inputs and outputs. I don't have the card yet, so I can't have Labview automatically detects, but I was hoping to get this code at the time he arrived.

Are there any drivers or updates that I need to install to see? Or is there a workaround?

Here is an almost useful answer:

I had the same problem. It turns out that you need to install a different driver. The problem is that I don't remember which driver. He could be in the section of the vision, or the section of RIO.

Hope this helps some.

Bruce

Tags: NI Hardware

Similar Questions

-

Carved frame. Camera Basler with FPGA

Hello!

I use a 340kc of acA2000 of Basler camera controlled by an FPGA PCIe-1473R.

After a few adventures, I finally changed and changed the configuration of TAP with this post.

http://digital.NI.com/public.nsf/allkb/EA1727D8D620B81F8625797B0072257C

With just the change in the FPGA, the camera works and takes pictures successful, however the framework is divided into four images (all identical but light intensity).

When I also change the host code, only an image appears in the frame, but certainly not a good image, as previously.

Someone knows why maybe this problem happening?

Thanks for your help.

I think I knew what is happening. I believe that section of the knowledge base that you read is incorrect. We will solve the problem together and I'll correct the article if necessary.

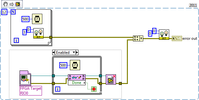

Let's talk for a little bit of what's going on. The two keys are 10 bits each, but they are stored in the 16-bit data type. The two pixels must collect the FPGA to the host with a DMA FIFO. For more convenience, the code uses a single DMA FIFO even if there are two taps. The article suggests that you must combine numbers 16 bits 2-in-1 32-bit number and then send it in the DMA FIFO. There are a few problems with this: first, the DMA FIFO has been configured for 16-bit, so half the data is being deleted. In addition, the code on the host computer is dividing the 16-bit data in 8-bit, which is not correct.

I think it would be better to change the DMA FIFO to support 32-bit data. You can do this by opening the LabVIEW project and right click on the host 16 DMA, select Properties, and then change the type of data in U32. After that, you must program the code on the host computer to divide the number. You will get then two tables (one for each). I think it will reconstruct the image correctly if Interleave you just these two tables.

I have attached a few images. Try it and tell me if this works. If so, I will update the documentation.

Jeremy P.

-

Cannot add to the target FPGA project

I installed labview 2010 with en FPGA in real time

In MAX under hardware, I see RIO0 under RIO devices.

I also installed NI - RIO3.0, that I can see in MAX.

When I try to add my FPGA PCI-7831R target in my project I don't see not all FPGA targets.

How can I add my PCI-7831R to my project?

LabVIEW FPGA and real-time 2010 require NEITHER RIO 3.5.1. NOR-RIO 3.0 won't the good support for LabVIEW to create targets in the project, even if the FPGA will be detected in MAX. You can install OR-RIO http://joule.ni.com/nidu/cds/view/p/id/2144/lang/en3.5.1.

-

I use a PCI-7833R FPGA, I know that it uses an FPGA virtex II FPGA, but I want to know the exact FPGA device used. See the attached table. Where can I find this information? I want to use the same thing with a 9148 with a Spartan II as well. Thank you!

Right-click on the target FPGA in your project, and then select Properties. In the General category, there is a field called target information. This is what it says for the PCI-7833R:

Target class: PCI-7833R

FPGA device information:

Family: Virtex-II

Type: xc2v3000

Speed level:-4

Package: fg676Jim

-

FPGA timing when compiling PID loop error

Hello.

I'm using Labview 2011 card FPGA PCI-7833R.

My problem is that whenever I try to integrate FPGA designed screws in my code, I get an error of timing. See the photos displayed below.

In this case, I have an express VI PID which I use in a used while loop (not even timed!) in my FPGA code, but when compiling, I get an error saying that the possible maximum clock frequency is the 43 MHz.

I have a lot of loops, a few running at 80 MHz. Is there a way to slow down a specific while loop, so that it runs at 40 MHz and not 80 MHz, as others? The compiler does not seem to meet the simple addition of a timer loop...

Thank you

Orel.

PS the same thing happens when I try to add a lowpass filter VI of the FPGA code.

Is it possible that you set the level above 80 Mhz clock? This is what it looks like to me. In Explorer, right click on the FPGA target, select Properties, then go to the category "first level clock.

-

[FPGA] Associate existing target FPGA with real hardware?

I started to write the code to FPGA and to support this, I have created a 'new' device FPGA - i.e. a device in the project but not associated with any actual hardware.

Now, a colleague has access to some real hardware and tries to run the code on this subject, but has resorted to the creation of another target FPGA from the existing FPGA device (real hardware) and copy of the hierarchy of the code of the other device 'virtual' on him. It is also having to copy/recreate elements such as FIFOs in the project hierarchy.

Is there an easier way to simply link the target that we created in the first place with the actual hardware?

Sorry, I thought that the question should pass a target FPGA to a project to another (existing) without having to recreate the FIFOs, clocks, and other resources.

If your FPGA card lies in a real-time controller you can simply change the IP address of the system in real time (as from real IP of 0.0.0.0 or any other intellectual property on the real-time controller) to run on a particular system.

-

Error when create control LabVIEW FPGA CompactRIO

I have error when you try to create a new model of LabVIEW FPGA CompactRIO control project. I tried with LabVIEW 2014 and 2014 SP1 update. This error always occurs.

Please help me with this.

Kind regards

Thang Nguyen

Hello

I fix the problem by removing LabVIEW 2014 SP1 and reinstall again. After the reinstallation of LabVIEW, I create the project template.

Kind regards

-

by deployed/launched RT App with "Open FPGA" no executable program

Howdy-

According to the instructions in these links:

http://digital.NI.com/public.nsf/allkb/A7DBA869C000B5AE862570B2007C4170?OpenDocument

http://zone.NI.com/DevZone/CDA/tut/p/ID/9640

and others I've read, I wrote a PC-side VI which FTPs a Source of RT dist. During my cRIO (9076), then use it "Run VI' method to launch the application.» For test purposes, the RT VI has a call option to a simple VI FPGAS:

With the FPGA disabled call, everything works fine. With the call of the FPGA, the method of "Run a VI" in the code PC side returns error 1003: "the VI is not Executable.

The cRIO VI works in interactive mode (front) with and without the call FPGA.

Any ideas why this happens?

I'm under LV 2011 on the PC and OR-RIO 4.0 on the cRIO. I've included with this post project files if it can help.

Thanks a lot and have a nice day.

Well, it seems that I had accumulated a bad bitfile associated with the FPGA VI (there were 2 of them in the bitfiles folder, where only should have one). The solution was to remove the old bitfiles and rebuild the FPGA of the project part.

-

PXI FPGA NI7831R Subvi nirviExtendedMemory.vi LV2011

With LabVIEW 7.1 projects, I had been using a Subvi memory, called nirviExtendedMemory.vi - it works like a memory "non-volatile". The Subvi is called by a 16x128block.vi. The subvis work together with LabVIEW 2011 on the host, but it breaks a LabVIEW FPGA 2011 because project as the "sub - VI 16x128block Subvi is not executable.

I'm new to LabVIEW 2011 - may it be resolved in the project FPGA configuration?

Thank you

John

Hi John,.

Can you give a little more information about the feature you are trying to reach? Would it not possible to post these Subvi?

Perhaps what you are looking for is the memory block. Try right-clicking on your FPGA target and selecting new > memory. Take a look at the "Memory check" section of this article.

Best,

-

Learn how to run labview vi on fpga target

How to create a vi and execute on the target fpga on labview? What are the boxes to tools/modules required for the installation and the steps of creating a vi to execute on the target fpga

Hello Wrang,

If you want to program in LabVIEW FPGA targets, you need following:

-LabVIEW

-Drivers for supported target FPGA (OR-RIO)

-in some cases, you must have the LabVIEW Real-time module (for example to work with ComactRIO)

To start working with FPGA targets, I would highly recommend to go manual start-up of pit for specific device. In general it's pretty much the same for all targets, then you can take a look at Getting Started manual with CompactRIO and LabVIEW.

You can also find a lot of documentation or examples on our web site. For example, you can take a look at creating a FPGA and Application project.

I hope you enjoy to work with FPGA OR!

Kind regards

s9ali

-

I am trying to stream as quickly as possible from the to a FlexRIO 7966 5154 digitizer. From the example "NISCOPE fetch Forever" in LV2012, I can implement the acquisition on 5154 @ 40MS/s, 50 k of data I8 piece and the graphical indicator seems to keep well indefinitely.

I tried then write data to an FPGA - FIFO target host, and it chokes. With FIFO write the method inside the loop of 5154 fetch the 5154 ends in error because of the "overwhelming memory" (it fills its on-board memory until the HOST is reading). With FIFO writing in a parallel consumer (queue conduit) loop, the queue overflows just because he can't write that as fast as the 5154 FIFO provides samples in the queue. What Miss me? The 5154 uses a PCI DMA bus (I think), so I think that if he could hold, the host to the FPGA PCIe bus must be capable.

There is another factor, that I have not taken into account? Sorry I can't provide the VI since the installation of the LV is on a PC not connected to the network. Any advice or suggestions would be appreciated.

Thank you

Mark Taylor

For future reference, I ended up resolving this by moving the implementation on the actual FPGA. I had run in mode "on the development computer with i/o simulated" and no matter what I did with the start-up or sizing FIFO sequence, it just doesn't work.

After compiling and running on the FPGA, all right. Maybe it's the basic knowledge, in fact I remember somewhere in my travels reading that don't accurately represent timing problems when running to the old fashion, but LV FPGA has kind of us painted into a corner with the compromise of simulation/compilation. They do not include Modelsim, which is the only tool that enables co-simulation do functional and verification of the timing set (we Questa, unfortunately) and independent VHDL simulation captures the interaction host with precision (and software processing/timing is impossible to quantify!). In my situation, the only way to operate at speed is in the FPGA, but then I can't see all of the things that I need to see to debug... ARGH!

Additional links and resources always will welcome (on debugging of FPGA LV and design in general). I found a couple of things below, which was somewhat useful:

"NEITHER powerful LabVIEW FPGA Developer's Guide"

http://www.NI.com/Tutorial/14600/en/

I found a link to an "FPGA Debug Reference Library": http://www.ni.com/example/31067/en/, but my installation does not seem to have this available.

And it looks like 2013 may add functionality to help alleviate some of this via the node of the execution of office referred here to the 'Test and debug LabVIEW FPGA Code'

-

Error opening of FPGA reference

I use the 8.6 and all the latest versions of the software on a device cRIO. In my code RT I opens a reference to a FPGA file and when I do with this error to expire:

error code:-63192

in Kyle.vi CRIO-CRIO Kyle.vi host

Activities FPGA:Open FPGA interface reference. in Kyle.vi CRIO-CRIO Kyle.vi host

There seems to be no explanation of this error on the Web site of NOR, and I need help to find out why the error might be involved.

OK, so I made a stupid mistake. The project I'm working on that uses 3 crios simultaineously. To simplify things, all cRIOs run the same screw on them and if necessary, they detect what crio they are on the fly.

Well, because all crios use the same file I had only opened the structure of files on the crio first in the project. The error occurred because I do not have the FPGA files in parts of the second and third crios FPGA in the project. Either they were removed or never added when I created a new project (created a new project to resolve a previous error). Thus, when the reference the the bitfile was attempted to be opened on the second and third crios, there is no FPGA files in the build, so he would give this error.

Quite embarrassing.

-

Limited to 127 for FPGA PID gain

Hello

I have tow questionq the first technical is the second commercial is.

1 * for an FPGA with PXI8108 and PXI-7841R application I want to insert a value of "2100" so greater than 127, but module of pid gain is limited to 127.

How can I do. Thanks for your help :/

2 * I want to buy another product like target FPGA PXI-8108 for other applications, but I need PXI7841R with LABVIEW FPGA and RT I only move forward without other complementary modules to insert. Is the chassis necessary?

I can't find other versions like PXI7841R do the same job with the same performance with PC but cheaper (no chassis & PXI-8108)? i ' am, search the Web, OR, but I have not found so can you offer me any product desired OR

Thanks for all your response.

Riadh WILSON.

(2) the chassis has the RT controller. You can get cards to USB (no RT) R series FPGA / PCI / PCI-Express that plug into an ordinary PC. You can install LabVIEW Real-time on a PC, but it requires some hardware configurations so that it can be supported. Have you considered a device of RIO as a CompactRIO / sbRIO? These are materials NI Compact integrated a RT and FPGA which are cheaper than the PXI controller.

-

Value of the loop 'For' pass before the complete loop - FPGA

Hello

8.5 LV, LV FPGA, PCI 7831-R FPGA Board

I got a cramp of brain on this one. I have a function (Arb. GIS read) that Im using to generate an arbitrary signal which I created in memory. I can't move to the value of data however. I don't know why I can not, its because it is nested in a "loop For" who runs indefinetly and updates only the value whenever it loops back to 'zero '. Ideas quick and dirty on how to use this value as it is being updated in the loop in my hand vi?

I've seen messages on the use of local variable 'Files' and property nodes, but I can not just give a sense the. Maybe because it's FPGA, something is different/no supported?

* My principal is 'control MicroMirror Arb. SP", look in the #4 case and the condition of"false. "

The 'Sub - VI' is called 'Arb Sig read RevB', and I'm trying to pass the variable 'Data' to hand while the loop For always runs.

Thank you!

-

can I set up an amplifier to lock using the PCI-7831 RIO map?

Normal 0 21 MicrosoftInternetExplorer4 / * Style Definitions * / table. MsoNormalTable {mso-style-name: "Table normal" "; mso-knew-rowband-size: 0; mso-knew-colband-size: 0; mso-style - noshow:yes; mso-style-parent:" ";" mso-padding-alt: 0 cm 0 cm 5.4pt 5.4pt; mso-para-margin: 0 cm; mso-para-margin-bottom: .0001pt; mso-pagination: widow-orphan; do-size: 10.0pt; do-family: 'Times New Roman' ;} "}

Hi all

I use FPGA, PCI-7831R module, I can implement locking an amplifier using the PCI-7831 RIO map?

Kind regards!

SUN

Hey,.

The following link shows an example of a lock-in amplifier set implemented on a cRIO with 9233 module.

-> http://decibel.ni.com/content/docs/DOC-1762

Hope this helps,

Christian

Maybe you are looking for

-

Satellite L500 pslkoa - missing network controller driver

I've updated my laptop L500 pslkoa-00r009 for windows 7 and I now cannot acess internet its showing that I have no driver for my network controller, I can not find the driver to download Where can I download the driver?All I have to do to solve this

-

When I print a page half page print, iam usig a hp photosmart c4680

What impression itry article printed using hp c4680 printer photpsmrt only part of the article

-

4 - 1212tu envy: UEFI problem in my laptop startup want 4-1212

When I disable legacy support more, it detects no boot option. Manifest error «Boot devide» not found So, I installed Win10 by setting the active support Legacy. It works very well. But I want to use boot UEFI mode what should I do now?

-

can't uninstall Kaspersky Anti-Virus 2010.

When I try to uninstall it a small screen that will display a so-called: Windows Installer Service could not be accessed. This can happen on Windows install is not correctly installed. Contact your staff to support im do not know what to do please gi

-

5745 Officejet HP e-All-in-one: bad disc

I've been unboxing my HP Officejet 5745 e-all-in-one printer it was good so far, but then I noticed a problem. The problem was that I had the incorrect installation disc. the disc was printer not e-all-in-one HP Officejet 5745 5740. I thought they m