Jitter in response to signal generator of digital dashboard by using trigger nor tclk with digitizer

I've written a VI that uses NEITHER tclk to synchronize a generator (PXI-5422 named FGEN1) and a digitizer (PXI-5122 named DIGITIZER1). There is also a clock card TIMING3 generating a digital camera.

It seems that can probably be explained by the way TCLK to synchronize, but I don't understand all the details. Could someone help explain this to me?

You are right. NOR-TClk ensures that all synchronized devices start at almost at the same time, to the same sample clock, with timing very tight. Sometimes, the level of synchronization with the devices OR TClk-synchronized beats at the level of the synchronization of the instruments of some competitor channels in the same device. But this is not free, there are compromises and added additional jitter for trigger response time is one of them. Here is an attempt to explain why:

When you use NEITHER-TClk and send a trigger, the devices will respond to relax on the next cycle of the clock once made the trigger signal to the device. Let's say you have several devices all of them even configured with the same clock frequency. You block the signal of PXI_Clk10 using their PLL, so they drift out. But each unit's clock edge will be off, clock +-0.5 cycles. If you send a trigger to each of them, they will respond on the next clock cycle whenever it is, after the arrival of the relaxation to each device with different propagation times, whatever they may be. You get a single clock cycle of jitter on reaction of device to set it off.

When you use NEITHER-TClk, several things happen: all devices are locked on the PXI_Clk10 signal to eliminate drift. The device clocks are then adjusted to a period level secondary clock. Very very tight. Then a clock signal common, slower called TClk is produced inside the devices. All the generation of trigger are delayed to be sent to the next rising edge TClk, and all consumption trigger is delayed to be received at the next front descending TClk. This way you make sure that propagation delays don't mean one of the devices does not react to the trigger until the next clock cycle.

That's why you see jitter above the reaction time of relaxation. When you add devices with different clock settings, so the frequency of the TClk can be slower for a divisible frequency in the device clock frequencies everything is possible. This causes the trigger jitter of reaction time be even slower!

I hope this helps you understand what you see.

Tags: NI Products

Similar Questions

-

Output a TTL HIGH 10 usec via the PFI port on AWG signal generator

LV dear community,

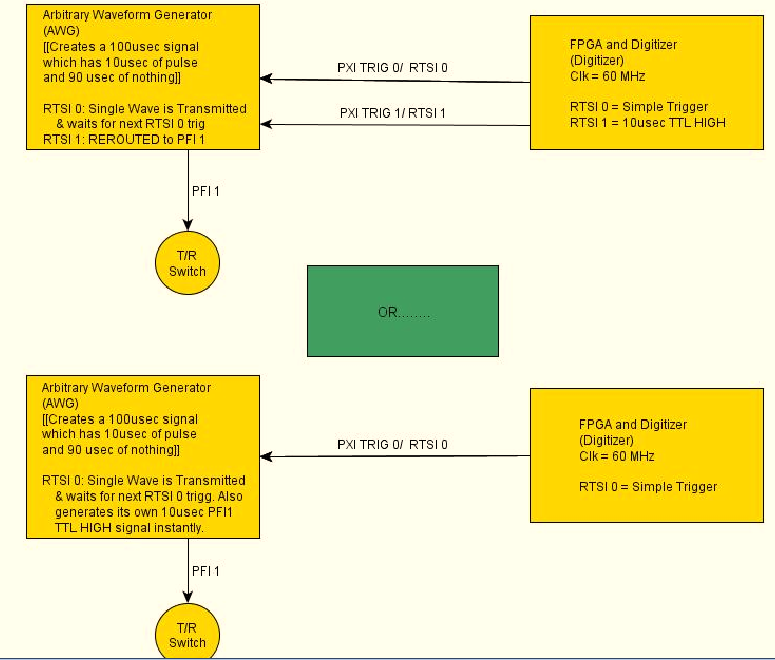

I want my signal generator (PXI-5422) to produce a pulse of 10usec with its PFI1 range each time that a wave of exit CH0. The frequency of repetition of the CH0 impulses and the port of PFI1 is 10 kHz. Is it possible for the signal generator automatically generate this HIGH TTL signals for usec 10 on the PFI1 line all at the same time produce a long-wave 100 usec?

Another approach, that I'm considering is to re - route a pulse of RTSI1 (10usec) from an FPGA and output via port PFF1 of the GTS. However, I doubt that this is possible, as the HELP MENU for the working group said that the report can only occur when the Working Group is in "idle" mode.

Any help will be greatly appreciated!

Have a nice day

I have attached a diagram of operation that hopefully, explains what I'm trying to do a little better. Once again thanks for looking!

I have attached a diagram of operation that hopefully, explains what I'm trying to do a little better. Once again thanks for looking!-Daniel

Hi Denn_Mann,

To get around the limit of 320ns, you should be able to use scripts with the FGEN markers to achieve your goal. Anything you want to do is use of script with markers in alternating mode. You may want to toggle high then low rocker after the number of samples you want pulse is high while your signal is present. I've linked some information below that should be good resources for script for you if you are not familiar.

Trigger on the arbitrary signal generators and advanced waveform sequencing

Creating an event marker in Script Mode

Script mode

Example of the expedition: "Fgen Arb Script.vi.

Kind regards

Ann Travis

-

generate a digital signal for 6722 or 6221

Hello

Thanks first for the help I'm already on this forum.

Now, I have the following problem:

I like to generate a digital signal: high for 300µs, low 300 µs, 300µs high, low 300µs, top for about 2 ms.

I'm looking for a solution how to generate this numerical sequence. At the same time, I will read the information via an analog input (if all goes well, I now have a solution for this problem).

I tried to find examples, but I failed. For the moment, I was not able to produce any numeric sequence that worked.

My hardware is 6722 or 6221 - which should be OK with respect to the calendar.

Thank you

-

How to control each channel of the signals emitted by the generator of digital waveforms?

Generator has digital waveforms of 8 channels. I need to generate two different signals for HSDIO. How to change and control two different ways? In addition, how to translate pinout of the PXI-6541 to channels? I need pin 1,3,29 and 31 control signal individually.

Thank you!!

You need to combine your personal data in a table. The digital waveforms is simply a numeric representation of the binary table. It always boils down to bit 0 of each element of the array will channel 0 (or the first string that you specify in creating dynamic channels). The next bit goes to the next channel. My last post is very clear. To display the table in binary, right-click on a table element, then select the display Format, then select binary. You can also right click on the element, select Visible, then select Radix Show to display the small b before the number. One last thing, in the display Format window, uncheck the box next to the minimum field width to use. Then set the digital just below zone 8. Then select Pad with zeros to the left in the box below.

You should not use waveforms up to what learn you more about how the HSDIO operates on the input data. It is not difficult to combine waveforms, but it is not as clear as it is using an array of U8, U16 or U32.

Trying to explain further. The first number to be written to the HSDIO will have this effect: Bit 0 (LSB) of the number is written to the first HSDIO string you specify. Bit 7 is on channel 8, you specify. If you specify no 8 channels, the bits download ignored. If wiring in a certain number will produce only a single bit on each channel. In other words, the number has already combines the bits of all channels that you specify. Combine you do nothing yourself. Return to my photo on my last post. By wiring in a table, you cause a binary model must be generated.

I hope that is more clear.

-

generate a digital triggering out CH1 (low and high) for the USB-5133

Hello

I would like to generate a digital triggering on the USB 5133 CH1, is this possible? I tried with the PFI 1 successfully but the output is only 3.5 v and I need to 5V, because this trigger signal goes to a box of pulse generates a signal, which is received by the CH0 on the USB-5133. This configuration works on the 5102 OR but because of the treatment, I am obliged to try a new device.

Channel 0 and 1 are only entries then you will not be able to use them to generate a signal. All of our products current digitizer that are recommended for new designs use 3.3V CMOS logic levels for PFI lines in output mode. Your best bet to generate a digital triggering 5V would be to use an external buffer that can accept 3.3V CMOS levels as an input, but is under voltage of 5V. Here are some that might work for you, but there are many others: http://www.onsemi.com/PowerSolutions/product.do?id=M74VHC1GT126DT1G adding a buffer in line with the trigger signal will add delay, so you will need to ensure that it is acceptable for your application.

Hope this helps,

-Matt

-

Generate a digital waveform like memory on PXI cards

Hello

I'm looking for a way to send a large digital waveforms using a PXI digital signal generator. I saw DIO HS cards, but their memory is smaller than the files that I want to transfer. My understanding is that the PXI backplane bandwidth 132 MB/s. So, I shouldn't be able to stream a digital signal from the memory of the card that is slower than the CPU? For example, 50 Mbits / second (equivalent to only 6.25 MB/s)? However, I think I understand after reading their textbooks is that you cannot continuously transmitting a large waveform of the processor memory file, you must transfer the file to the memory of Council first and then transfer that out.

Does anyone know if there is a way to have a flow of digital signal generation card an arbitrarily large directly from memory to the processor of digital signals? Or, what is the fastest card of pxi digital signal generation that does not require the storage of Council first files?

Thank you

Isaac

Hello Isaac,.

Take a look at the following area developer.

NOR-HSDIO Stream from disk (generation) using Win32 file IO

Note that you will not be able to take full advantage of the maximum rate of update HSDIO devices, because the data must be transferred in a bus. Some other considerations are the width of the data as well as the HSDIO device you select, which may depend on other requirements not related to the size of file or waveform (for example the standard voltage or whether you need hardware compare). For more information, take a look at the developer following items area.

Data streaming of Architectures in the PXI systems

The use of National Instruments Logic Analyzer and generator of test patterns SolutionAdvanced features of e/s high-speed digital devices White Paper Series

-

Why can't I control my LabView signal generator?

Why can't I control my LabView signal generator?

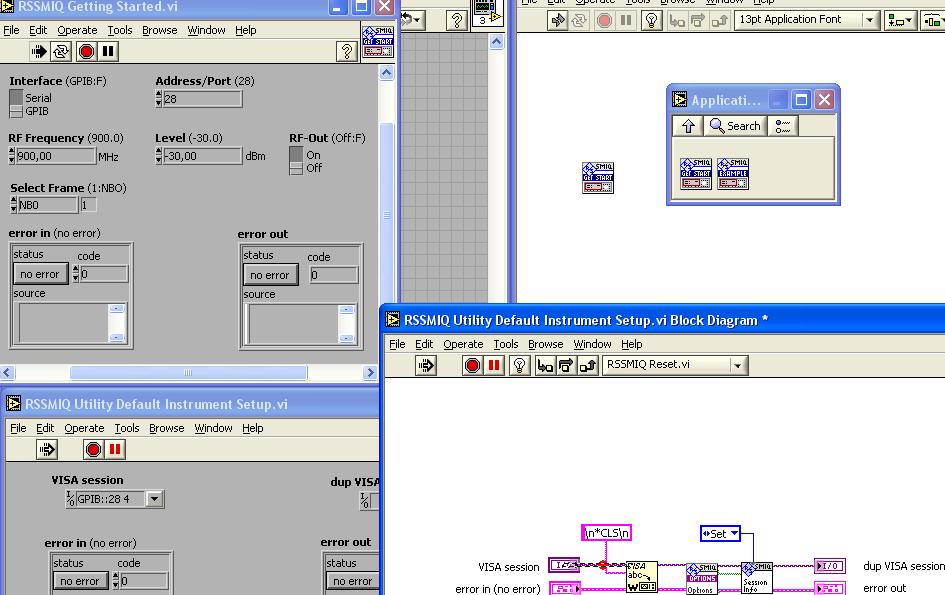

I put in schema-block function RSSMIQ (a function of the driver for my generator). I click on the RACE of VI, but compare a (red dot) interruption between the VISA ABC and ABC VISA and VISA SESSION flash icon. Why?

Automatically, it is open RSSMIQ DEFAULT INSTRUMENTS SETUP UTILITY and compare the figure downwards:

Is that a mistake? What? Why? I have fought with my generator WITHOUT ERROR?

Please see my response to your other post response No. 26 .

-

Wait signal generator complete the scan list before sending the next command

I am writing a program for Agilent E4421B signal generator scan to list between a range of frequencies (ramp up to the maximum frequency and then back down to the original frequency) specified. The signal generator has only a list of 401 points, which is a problem when I want to wash over a wide frequency range. To work around this problem, I would like to perform several scans of list in a row. However, I can't figure out an effective way to "say" the program to wait until the previous scan has finished before sending a new order of scanning for the signal generator. Any ideas? For reference, I use Agilent ESG drivers series LabVIEW.

Thank you!

If you use standard VISA calls, I would say just that send the scan command, but add; * mutual fund? (operation ends?) make a query. Then, run a VISA to read what's coming. This indicates to the device to send a 1 to the output buffer when the scan is complete (or just about any other operation, also). As you are waiting for a response, your computer will wait the amount of time to wait so he could see a response, it is not less, your way with the exact amount of time - no more - to be actually taken.

A few warnings:

(1) make sure that the time-out is longer than the length of most slow scan.

(2) there are variants of the '1' being returned. I saw '1', '01', and even "1.00E + 3" therefore to allocate more than one byte to read."

-

pulse width of measurement of signals generated by data acquisition

Finally, I would like to:

Start a counter pulse width measurement and the analog output at the same instant.

Stop the measurement with an external digital signal pulse width.My current plan is to use a digital output on the acquisition of data to synchronize a digital input and the start-up of the meter input. The digital input will be a trigger to start for the analog output. This works, except for the meter.

While trying to implement this, I tried a simple test to generate a digital pulse with the acquisition of data and wiring for counter inputs. It does not, even if it seems perfect to an oscilloscope. Then, without changing the software at all, I connect a function generator to my counter entries, and it measures pulse flawless widths.

I'm actually implemented it with a Python wrapper around the C DAQmx API, but I recreated in LabVIEW, and it has the same. VI attached. I have the latest drivers DAQmx.

Accidentally, I posted this in a forum for LabVIEW, as I managed to post with the account of a colleague. I think 2 ups live as this mandate to another post. I'm sorry. Former post is http://forums.ni.com/ni/board/message?board.id=170&message.id=389856.

Solution: I had to set the channel to counter with implicit synchronization. In addition, the sampsPerChanToAcquire must be at least 2, if not, there is an error. I still don't understand why it worked with a source of external impulse, however.

DAQmxCfgImplicitTiming (task_handle, DAQmx_Val_FiniteSamps, 2)

-

With the help of the external RF signal generator

Hello.

I just want to ask how can I remove the frequency shift if I use an external RF signal generator (instead of the RF PXI-5652 signal generator module). I understand that in the case using the OR to generate RF signals, frequency shift is deleted by setting the same source of reference for the transmitter and the receiver clock (placing the clock source of reference to PXI_CLK of the façade of generation VI and VI of the acquisition).

Thank you very much.

Hi Betty,.

In this case, no changes are needed, such as modules OR still use background clock basket PXI as the ref. clock source If you are still having a frequency shift, you probably need to configure sig gen to lock a clock external REF. Usually, just make the connection of the signal is not enough - you must also indicate the sig gen to use the signal connected to the input clock ref. Terminal

If you use the sig gen as clock source master Réf, connecting the 10 MHz of the gen of GIS at the BNC 10 MHz IN on the back of the PXI chassis replaces the clock native from the newly connected with the PXI chassis backplane, and analyzers are still using the clock background basket PXI as the source clock Ref (no change to the SW settings).

Kind regards

Andy Hinde

RF systems engineer

National Instruments

-

Hello

I want to do a continuous waveform. There are samples and files online to do it, but I would like to be able to change the frequency of signals continuously, I mean something like a function generator. I try to use the channel of PFI in NI 6221, but it provides just the waveform with a constant frequency. I wonder if it's a good idea to use the channel of the IFP? I want to give 100 kHz square wave.

Thank you

Hi Saridar

Thisexample may be what you are looking for!

Concerning

-

How to generate the digital output of the variable duty cycle and clock source being contrary?

I want to generate a digital pulse every front amount of my pulse counters. He must have a variable duty cycle. until now, I've been able to generate a digital output, but I can't change its duty cycle.

pls tell how I should proceed?

Thank you in advance...

-

calibration of Agilent N5183 Signal generator for specific output level

Hello

Newbie to labview environment! I'm writing a VI to calibrate Agilent N5183 to a specific output. For example if I want to have-4.5 dBm output of my installation (as stated on my electricity meter) I'll have to set the sig gen to say 7 dBm given my losses, etc.

How can pointers, I start to weld it? I think I'll have to create a while loop to check the levels of power, but I don't know how to increment and decrement the amplitude of sig gen and stop at the desired level!

Thanks in advance for any help.

PS: With the help of Labview 2013, on win XP!

mkossmann wrote:

3. adjust the pout to sign Gen to the desired level, while controlling the power power meter

Why is it that step at all? It is not clear from your description, what makes the difference between the reading of the gauge and the output level of the sigGen parameter.

I have done many times. Especially in the RF field, you want your tests to have a certain level of power to the object to be measured. We therefore have to adjust your signal generator to compensate losses in cables, couplers, etc.

To do this, all you have to do is set your generator to the desired level. Then measure with the power meter. Subtract the measurement of the desired and add that much more to the output. Repeat if necessary. I advise to use a conditional TO the loop so that you can easily set a limit to how many times adjust you (I've been in infinite loops due to the weird situations here).

-

How to generate a pulse with the signal generator?

Hello

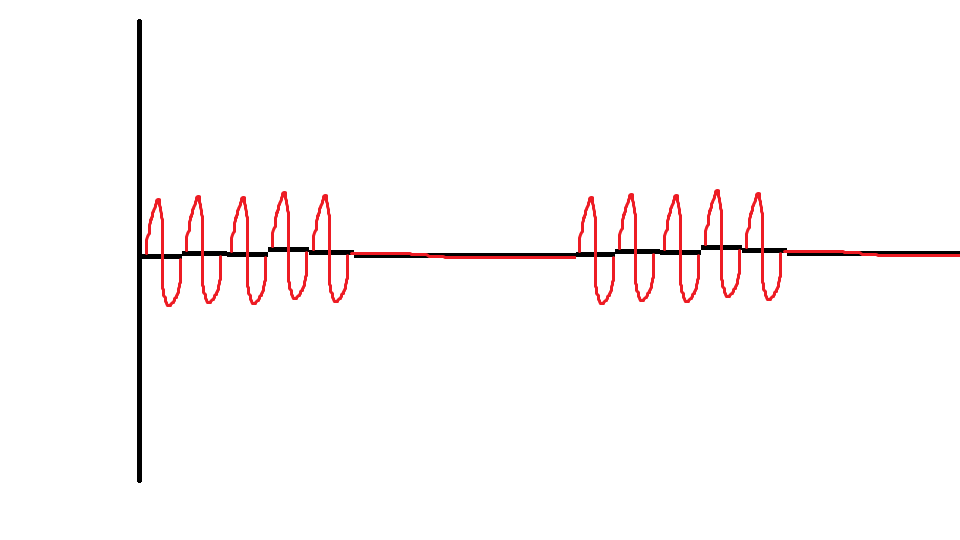

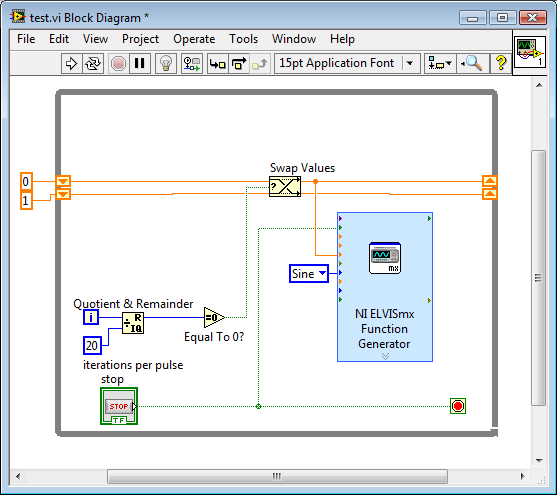

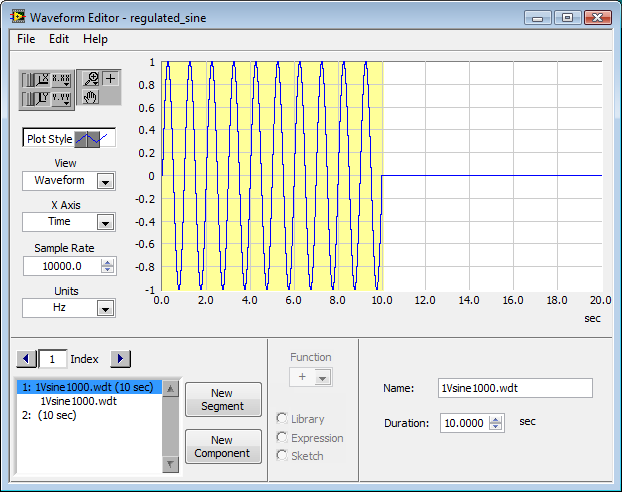

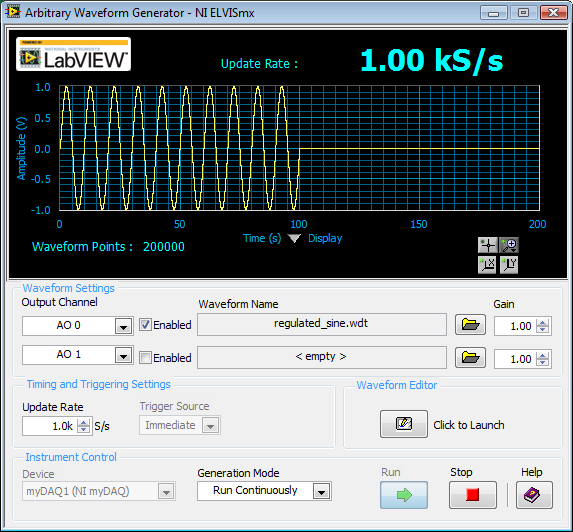

I would like to ask if anyone knows how to use the Elvis platform to generate a regulated pulse wave?

It should look roughly like the picture above. A sine wave with the regulation.

Anyone who can answer my question please respond to my post.

Thank you.

You are using LabVIEW to generate the waveform or using the Soft front panels? In LabVIEW, you can use the express VI generator function and specify the Type as "Sine". Then, simply change the amplitude of the sine wave. During the actual pulse, the amplitude would be what you want (i.e. 1 V) and while the pulse is idle, set the amplitude to 0.

If you use the soft front panels, you can use the Waveform Editor to create a waveform that includes a sine wave for the length of your pulse and then the values of '0' for the rest of the time. Then use this waveform in the flexible front of the arbitrary signal generator. Simply create a component of sine as the first part of the wave and then add another element to a level DC '0' for the rest.

-

[FPGA] Problem with the sinusoidal signal generator

Hello!

At first I want to apologize for my English is not my mother tongue.

Hardware and software I use is:

LabVIEW 8.5

NEITHER RIO 2.4.1

NEITHER cRIO-9014 (controller in time real CompactRIO)

NEITHER cRIO-9104 (chassis and FPGA)

NEITHER 9264 (16 channels, +-10V, 16-bit voltage analogue output Module)

I made a very simple FPGA VI: a while loop, generator of sinusoidal signal and a FPGA of e/s node in the loop. I've specified the Gnerator settings by following the path:

Frequency = 50 Hz

Amplitude = 1

Phase shift = 0.00

Size of the table look-up = 1024

= 16-bit amplitude resolutionFPGA clock frequency (40 MHz)

But the wave of "sine" I got is not what I wanted to get. First of all, its amplitude is 1 V. shouldn't it be coded on 16 bits? If I wanted to get 1V I should have specified Amplitude as a 3277. In addition, 'sine' is not very detailed, it's look like "steps", as many samples vere missing. What I did wrong? I checked the samples and tutorials, I did everything the same way. A I forgot something or not has not specify other parameters?

Thanks a lot for your help!

OK, I solved a problem. It's embarrassing to admit, but maybe this will help someone else

I blame my inexperience

I blame my inexperience

The main solution to the problem was changing calibration of calibrated RAW Mode. After that, everythoing works as expected. I had a problem with a sample because I was using a multiplier to control the generated sine wave amplitude. But... She was set to 1 in the sinusoidal signal generator. That was the reason for waveform Gradin. Please, don't laugh too much

In any case, thank you for an answer! It is now resolved

Maybe you are looking for

-

For past month or two, when I consult Wikipedia a few other sites, sections of text are displayed in a large, cursive font. I can't find any rhyme or reason to what sections show this way. This isn't the case at all sites but there are a couple where

-

Cannot initialize the Satellite L300

I hope you had a great Christmas, I am new to laptops, I got one for Chrissy, but cannot have running, When I turn it on I get a box saying; The computer began to quit unexpectedly a posted and unexpected mistake. Windows installation box does not, t

-

Reactance frequency-dependent in the definitions of materials

I'm trying to run a simulation for a material with a reactance frequency-dependent. However, when I try to enter a variable for the frequency in the definition of material I receive the following errors: Global definitions21:50:04 frq - error of the

-

What is the hex code of the modern green color used on the cover of the Microsoft Manual of Style?

What is the hex code of the modern green color used on the cover of the Microsoft Manual of Style, 4th edition? original title: Going Green...

-

Start options menu appear in the taskbar - how to display the Menu start properly again?

One of my students has somehow managed to get all its options of Start Menu in the taskbar. The Start Menu does not pop up as it should. I tried to fix the problem using all conventional means relating to the Start Menu and taskbar in properties, b