Timed loop closure problem

Hello world!

I'm working on a project with more comlex VI included, and I have some problems with the closure.

I want to manage a statemachine Central stop, here I get a Notifier and send a bool cluster. The first element of the bunch is true if the closing process can begin, and then all VI before actually writing the corresponding element of cluster true, so ultimately I can check if all VI had wound up down correctly.

It goes perfectly with each VI written by myself, the problem appeared when I tried to change third party VI. The VI is required, this is the original watchdog of a motor controller, so it is not possible do not use.

So there is a TimedLoop in this VI, and it seems that the TimedLoop the Notifier is not refreshing itself inside, so I don't have the chance to stop him.

Can you give me some advice, what tool could I try to use to give a command of the machine of the State of closure?

Thanks in advance!

In the meantime I discovered that there was a problem created by myself outside of the VI.

Thanks for the help!

Tags: NI Software

Similar Questions

-

Normal 0 false false false fr X-NONE X-NONE / * Style Definitions * / table. MsoNormalTable {mso-style-name : « Table Normal » ; mso-tstyle-rowband-taille : 0 ; mso-tstyle-colband-taille : 0 ; mso-style-noshow:yes ; mso-style-priorité : 99 ; mso-style-qformat:yes ; mso-style-parent : » « ;" mso-rembourrage-alt : 0 à 5.4pt 0 à 5.4pt ; mso-para-marge-top : 0 ; mso-para-marge-droit : 0 ; mso-para-marge-bas : 10.0pt ; mso-para-marge-left : 0 ; ligne-hauteur : 115 % ; mso-pagination : widow-orphelin ; police-taille : 11.0pt ; famille de police : « Calibri », « sans-serif » ; mso-ascii-font-family : Calibri ; mso-ascii-theme-font : minor-latin ; mso-hansi-font-family : Calibri ; mso-hansi-theme-font : minor-latin ;}

I experienced a problem with an application. I think I've isolated the problem in the "Timed loop question - Source Code.zip" attached source code. A detailed list of my results are in the attached document "Timed loop detailed question - Results.docx.

Overview - it seems to be closely related to the IO files and the use of "Timed loops" on the OR cRIO-9012

1. If I activate the e/s in two loops, then two loops crash simultaneously

2. If I activate only the e/s in a loop, then only this loop crashes

3. If I activate the e/s in two loops and make a 'While' loop earrings, then it don't crash

4. If it is wrote nothing in the file I/o, then it don't crash

5. If the reference to the file is left open instead of opening and closing on each call, so it don't crash

6. If I try to run it on "My Computer", then it don't crash

7. If the IO is only activated in a loop and programmed to wait for one second between the file access, then it always crashes

In my real application, any given row is only writing (at least) once a minute, but I couldn't still my application to plant within a period of 24 hours by writing a single error of a single loop once per minute, with a low CPU use. It was the impulse to test the seventh point above.

It seems that the best solution was to open the reference to the file and let it open. I think it is a good practice in general and I'll do the update in the application. This should solve the problem, but it is very difficult to verify this due to the sporadic nature of the question. As such, I'd like to understand what was causing the problem so I can verify that it was fixed. So far, my attempts to create a single, coherent theory able to explain all aspects of this issue have failed.

I just wanted to know at all that there has been a request for corrective action (CAR #214156) has filed for this issue to be fixed in a future release. This seems to be a problem with the VxWorks operating system, we use in real time. We have additional cRIO chassis which have a Pharlap OS where it does not work. For now, you can search for this CAR ID notes to see if this problem has been resolved for publication in the future.

Currently, there are two solutions, we have identified for this problem:

1. open the file before the loop and close it after. (recommended)

2 perform file i/o in a normal loop and transfer data to a queue. -

Timed loop continues to turn after stop

Only, I have seen this time, but thought I should ask about it. After pressing the stop button, I was surprised that the diagnostic LED on the front panel of the main vi kept flashing. With the performance highlighting ONE values showed that the timed loop was still running. I checked the other 8 loops clocked subvis and they also ran. None of the methods Stop worked. Only stop LV and abandonment of the cRIO eliminated the problem.

Run LV2014 SP1 on cRIO-9067 with dual-core ARM processor. Windows 7 x 32.

BTW: The function of the check LED VI scale does not work on this device.

You must allow an order any to be able to stop your curls. A simple global variable would work well here.

-

Hello

I would like to create a FPGA loop that runs at a fixed rate. Whatever if I use a timed loop structure or a timer loop express VI into a regular while loop? Under what circumstances should I choose one over the other?

I understand that the timer loop approach can cause the code in the loop run twice before calendar is established (but this isn't a problem for me here). Are there other differences in the two approaches?

Thanks in advance.

JKSH wrote:

But my question was about the differences between the use of "multi-cycle" Timed loops and VI express loop timer.

In a targeted FPGA VI, all call loops are single cycle timed loops (SCTL). This means that all the code in a SCTL must run in a clock cycle, so there are a few types of nodes cannot be used in such a loop. In a used while loop with a timer, you can use a wider range of features, but the loop will generally run much more slowly.

These documents may be useful to learn how to use loops clocked on FPGA:

Using loops of Cycle time unique to optimize the FPGA VIs

Optimization of your screws of LabVIEW FPGA: running in parallel and Pipelining

-

Timed loop in loop of producer/consumer

Hello!

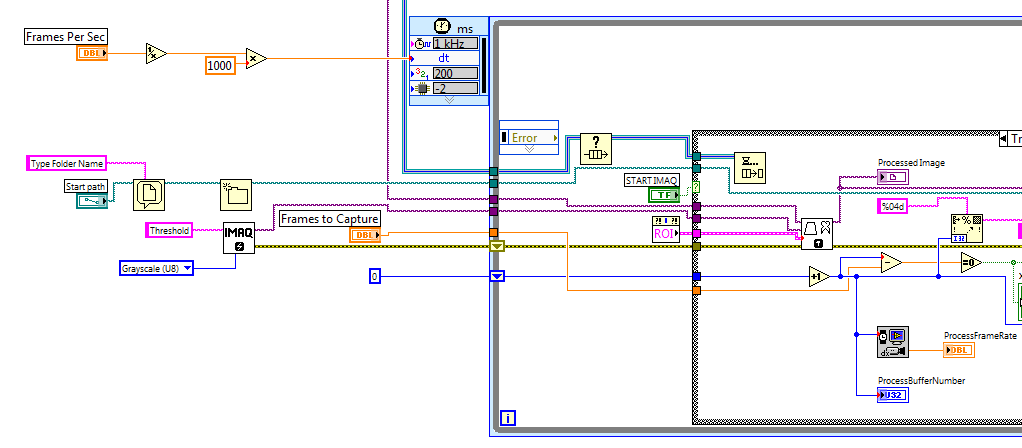

I have a loop of producer/consumer LabVIEW program configuration to allow me to properly capture the images that are large enough (8MP) at about 14 frames per second (FPS). The program works very well when the consumer loop is a while 'loop' (recorded at 14fps without problem), but I wanted to do a loop timed, so that I can vary the FPS as requires it. A curiosity arises when I do that. Anywhere under 12 fps, the loop works very well and the data is saved correctly. However, when I bump it up to 13fps, the calculated consumer FPS goes haywire and starts to jump between 9 ~ and ~ 13fps (processing of data gets bogged down?). When I set the FPS at 14, the loop runs at a constant maximum 7 fps. Is there something I can do to remedy this situation?

I have attached my .VI

Thanks in advance!

Palanski,

Are you using LabVIEW Real-time? Loops clocked to a windows OS do really increase determinism more than a while loop with a wait until the next timer multiple. Before you change the loop of producer-consumer in order to include a while loop was programming works correctly? You can also vUtiliser the VI analyizer to see how long things take to run. I let the loop of consumer to the producer in the traditional game upward and change the FPS by controlling the timer to wait, after benchmarking your code, it should be done in the same way as you did for the timed loop

-

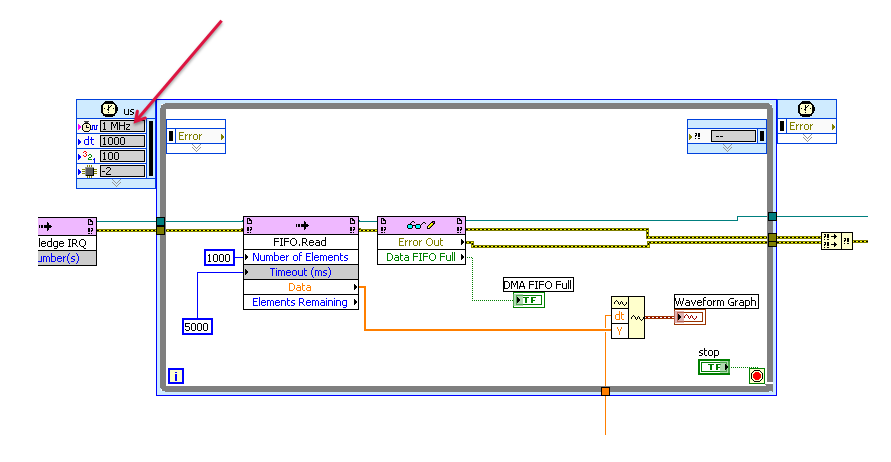

I have two codes for my NI9024 cRIO; an FPGA and a side side of RT.

In my RT code, I use a frequency of 1 MHz for my timed loop.

Just wanted to check if I should consider certain things important when using this frequency or not.

I mean, is there a particular point or referring to the fact that I had noticed.

Is there any limitation, future problem or question?

Just to be careful.

I think that the point that you are missing, it is that it is never necessary to update a graph 1000 times per second! operators just can't see that fast! So, unless you save the data on a disk, you can use a much slower pace of update. You can indeed, be limitation in this loop timed by your actual acquisition rate (timeout is 5 seconds - what is the sampling frequency of the FIFO?)

If the buffer is full or reduce the sampling frequency of the FPGA (a million points per second is really much more that a human eye can process) or increase the number of samples by reading.

-

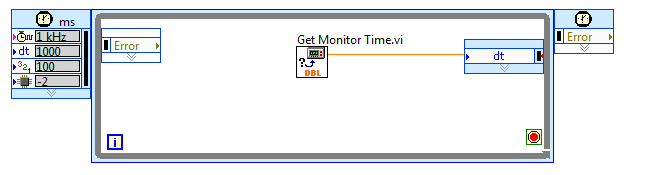

How to force a new period of a timed loop?

Hello.

Here my question:

I need to modify programmatically the period of a timed loop. This isn't a problem but:

I have to wait until the next loop to present new period value. For example if my previous period was 20 minutes, now I have to wait 20 minutes in order to submit a new period.

This beacause the code to change the period should be inside the timed loop itself. You can see what I mean in the picture as an attachment.

The Subvi Gets the new period of a console operator. It will run until the end of the period previously configured.

My question is: is it possible to force the timed loop to get the new value without waiting for the execution of the previous period?

Thank you

FPIA

Hi fpia.

Sometimes, it would be more useful to 1200 seconds instead of 20 minutes

It was suggested many times before: rather than wait for a long time with just a single call to a wait function you should divide this amount of time into smaller pieces!

-Why do not use you a period of time for example 5 and only count the iterations to know when 20 minutes are more?

-Why don't you use the function "Time" to know when to exceed the 20 minutes?

-

Sequence structure flat inside the timed loop and execution order

I have some problems trying to implement a flat sequence structure when you use a loop timed on a target of cRio VI

I tried with or without the while loop around the structure of sequence flat, and I also tried to replace the 'Non-deterministic loop' with a timed loop

The problem is that the program seems to run only once, then get stuck somewhere

I am writing a program that performs the following operations as soon as possible:

1. read the Pos_MC of entry on the FPGA

2 send the value of Pos_MC to the VI target (on cRio CPU)

3. calculate a value of output based on Pos_MC with a PID block ("exit PID')

4. send 'PID output' to the FPGA

5 write "PID output" analog output "MOOG".In addition, I want the program to return the measured value "Pos_MC" to a host VI for the recording of data

So that the output of PID is calculated and sent to the FPGA as quickly as possible, I placed a flat sequence structure to ensure that it happens before you send the output to the nondeterministic loop for recording data

Also, I want the digital input 'Stop' to be able to stop the loop deterministic (the timed loop)

I read much more entries than that and the help of several PID and exit, but I rewrote the code for a single entry and exit to make it easier to illustrate

Screenshot of the code is shown in 'target code.png' and 'fpga code.png.

The VI themselves are attached in the next post (cannot attach files of more than 3)

Question 1:

Any advice on how to get this race? Thank you!Question 2:

Is also my correct understanding in that, using this structure, each 0.9ms (fpga loop time) comes the following:

1. the input ("Pos_MOOG") is read on the fpga

2. the production of PID is calculated on the cRio with some delay to computation (for example 0.1ms)

3. the output of PID is then written for analog output "MOOG" in all about 0, 1 - 0.2ms

4. the FPGA program then waits until 0.9ms spent and repeat the processAs opposed to the next pass whenever performing a loop is started on the FPGA:

1. the FPGA reads the input and written on the output (the output of the execution of the previous loop PID)

2. then the entry is sent the cRio, PID output is calculated and sent to the FPGA

3. the new release of PID is maintained until the next time through the loop

Thank you!

PHG wrote:

Thanks for the input guys, any advice as to how I could get the feature in scenario 1?

I still say that the best route is just putting all the logic of the control in the FPGA.

Other alternatives include 1) the use of DMA FIFO sedn data back or 2) use interruptions so that the FPGA code can not read the output level until the RT.

DMA FIFOs are usually very limited, and I would not use them in this situation since I belive said it this code to do for the many outputs.

-

Having a strange action case structure on a timed loop.

A resolved question yesterday, lead to a new problem. In this VI, I have a timer that triggers an external meter. The counter "counts" from 1 to 24, each with an action at a given time. However, once I got the timer and counter work, I found that the Boolean trigger remained on the hour enitre, and my action was repeated several times instead of only one. So, I changed the counter count 0.1 each interval, rather than 1.0, thinking that it would only allow my State business to operate for a shorter window. However, when I run the VI, the case of the State are active in the meantime, not at the interval. For example, cases of stae 2 is active between 1.5-2.5 iteration and iteration throguh 2.5 3.5 State case 3 is active. Can anyone suggest how to get either 1) better display resolution on the evidence of the State of th or 2) another way to get the Boolean value for just a few seconds?

Thank you, Lynn. Yep, I tried that (at least the half of it.) I opened it in my first version, which is being 8.5.1. I don't think to check in the dialog changes not saved, however. I feel kind of sheepish having never tried that before.

Well, here is my interpretation of what was asked for... I had to make a few assumptions, namely that the 'timed loop' refers to the while loop that runs at a defined interval, and that "triggers" are just the Boolean flags.

I hope that this at least partially answered questions?

Jim

-

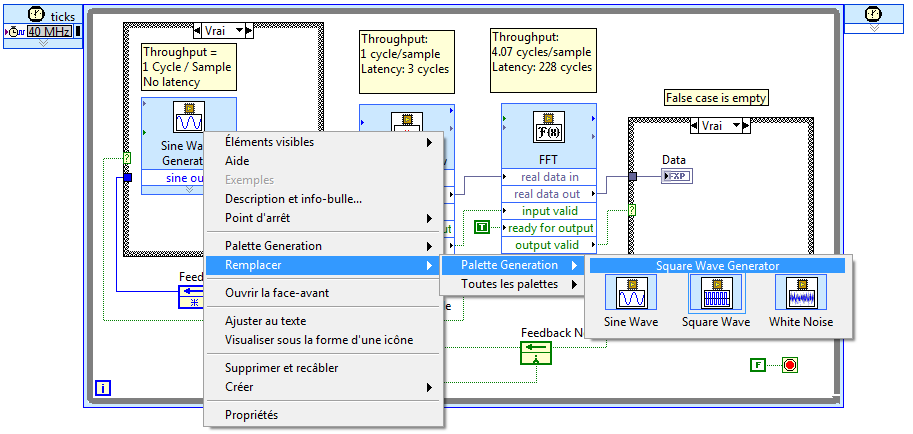

FPGA 2012 training: exercise fails '4-Wire Protocol' 7-2: not supported in single-cycle Timed loop

I work through the training courses OR 2012-FPGA with Labview 2014 SP1. I find the solution provided to exercise 7-2 called '4 son Protocol.lvproj' does not work. He is unable to run with the message "LabVIEW FPGA has reported the following error: item (s) not supported in single-cycle timed loop.»

Should it? I thought that the examples in the solutions folder were supposed to work such as provided. What needs to be fixed for this work? Thanks for any help.

Hello jbeale1,

It is a known problem. Here is the comment of NEITHER:

---------------

Exercise no. 7-2: 4 - Wire Protocol [Allen Hsu 2013.8.19]

- Description of the problem: exercise 7-2 uses a sine wave generator inside a SCTL VI. In 2012, LV, this VI is not supported in the SCTL, but LV 2012 will allow you to use mode 'simulation' (run on the dev machine). However, LabVIEW 2013 not even lets you use this VI in "simulation" mode If you run the VI with the sinusoidal generator inside a SCTL VI, LabVIEW 2013 gives you a "or objects not supported in single-cycle timed loop.

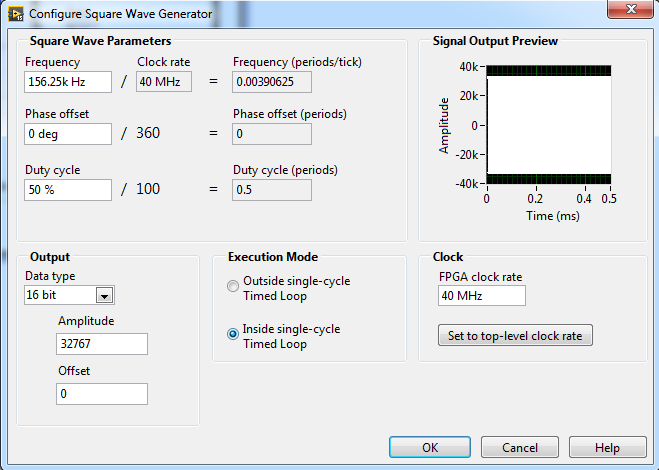

- Solution: If the students use LabVIEW 2013, you must tell the students to replace the sinusoidal generator inside the SCTL pre-built exercise VI VI with a Square Wave generator VI with the option "inside the SCTL" enabled in its configuration window, as shown below:

--------------

To replace the "sine wave generator" right-click on it and select the 'Square Wave Generator'. Then you have to double click on the "Square Wave Generator" and select "inside the only cycle timed Loop". You should then be able to run the example.

-

Most of the machine control software I design have the following structure:

1. There's a HAND that takes place inside a TIMED LOOP with synchronization of 50ms and priority of 100. His only job is to read / write data from / to DAQMx IO cards.

2. the MAJOR can call several SUBs based on the choice of the user, and once a submarine is called FP MAIN is closed and the FP SUB opens. All submarines have a States Queued Machine running within a TIMED LOOP with 50ms timing but with priority to 50.

3. data transfer between HAND / SUB is through function globals - there are many of them based on past data.

4. all woks fine so far. No need to any RTOS. and platform of WIN7 is alomost standard. I even ran with a timing of 20ms without anything crashing...

Problem: When there are a lot of file i/o operations in a SUB partciluar, then I have the chance to see several missed iterations. Perhaps the TIMED LOOP is hogging resources.

What I want to do: convert both TIMED in asnd SUB HAND loops simple while loops. But I am concerned by the priority - since the MAIN interacts with HW there priority. But with LOOP WHILE how can I ensure this?

Or is there any replacement / effective way of doing what I do now?

Rama wrote:

.... FGV should be thrown out the window...

Well used for a while, based on many articles in the KB. One of them is locked... and it does not represent the engine of the Action or of the FGV as a villain to avoid.

The driving force is one of the largest buildings in LabVIEW. The FGV who does nothing but Get and Set (or writing and reading) is useless and a waste of resources. Why? It does nothing to fix possible race conditions (does not protect critical sections) and it is much slower than just using a global variable. See this example I put in place to see what I mean: an overview of the race Conditions.

Rama wrote:

So in the sample that I had attached, what do you think would happen if I just replaced the two loops with the SAME timed in MAIN and SUB wait value ms. is there a work order then?

When things are at the same time, there is no such thing as the order of execution. But as I said, it seems that your loop is quite slow, so it's something I would not worry. Just make sure that you do not have a loop that uses all the CPU.

-

What happens if my computer cannot process a pretty quickly timed loop?

If I created a loop timed, but required that more important than my computer treatment is able to do before the next iteration the tasks within the loop, what happens? It gives me an error or I miss loops? In the end, I need to know how can I know if the problem occurs.

Please see the setting the Mode of a section of the loop timed in the following document.

http://zone.NI.com/reference/en-XX/help/371361F-01/lvconcepts/configuring_the_labview_timed_loop/

The left consider the following section describes the information that you can access on the previous iteration of the timed loop.

http://zone.NI.com/reference/en-XX/help/371361F-01/Glang/timed_loop/

-

Why extend a timed loop always expands diagram in the same direction?

I just noticed a behavior of wiring diagram in LabVIEW 9 I love not really for. I have several parallel call loops on my diagram and want to do a little to add code in their breast. When I drag one of the other side to expand it, my whole wiring diagram expands to accommodate the drag. However, when I am developing one of the others in the newly created space, she AGAIN extend my digraph together in the same direction. Why do what there already is plenty of space to expand to created by the first operation "click and drag". This problem can be avoided? If so, how?

Bill

Ah, the forum of OR is a source of deep wisdom and knowledge

Please read this thread for a solution.

BTW. you don't need programming/reset this option each time if you want to only timed loops to have this disabled. You can set this option by the structure after a fall by using the context menu.

Norbert

-

I have a timed loop that monitors the equipment. Whenever there is an error I send a notification by e-mail. My problem is how to stop send e-mail whenever the time loop is executed. I tried placing email it inside a loop, but quickly realized that the whole of the loop itself is reiterted. Any help is much appreiciated.

You can also consider using the first call? under the range of synchronization primitive.

-

passing the value and to timed loop

Hello everyone,

I'm working on a VI that consists of a timed loop which takes values in a file every 6 ms and writes it to an output file. Inside this timed loop, there is also a MATLAB block that calculates a parameter based on the value. based on this parameter, that a marker is set to 0 or 1 (planned) to operate as a Boolean marker.

The problem arises when the marker is set to 1. I need an additional structure any that waits five seconds (without stopping the timed loop iterations) and a 'stop' button is not pressed an additional string is placed in the output file. I wish for the marker to get back to 0 if you press the 'stop' button and not string to put in the file.

The main problem seems to be the use of a structure outside the timed loop. I can't have a while loop or any structure that waits 5 seconds inside the timed loop. And if I let him out he does not have the value of the marker second structure during execution of the timed loop.

+ Any ideas on what the structure to be used during the 5 seconds Timeout? (I tried a while loop)

+ Use a local or global variable for the marker? (I tried briefly, but as a local variable, I couldn't choose a variable defined in the MATLAB block, and I don't understand global variables in LabVIEW)I enclose a simplified version of the VI as well as a sample input file in case it can help visualize.

Thank you

DAVASo far, there are a few problems with your solution, but first of all, I will try to help answer your original question.

You are right that you can't have a structure inside the timed loop which waits five seconds without blocking execution of the timed for the same period. You are also right that you cannot simply communicate through cables to an external structure. If you exit a loop of wire in the other, which creates a dependency of data flow, which means that the data loop cannot run at all until another loop ends its execution entirely and send data.

You have two options:

- Don't actually use a wait function to determine if the 5 seconds elapsed. Use the Express VI of time elapsed (search the palette). He just guard track of how much time has passed since the last reset. It does not wait. If you are safe to use inside your loop timed in a case that is triggered when the marker value becomes 1. Also check the Boolean command in this case Structure to decide if you should output the data in the file.

- Use an outer loop as in the example you posted, but use screws of the range of synchronization to send data between the parallel loop. Consider a queue.

But overall, I don't think there is much chance of this work very well. No way, the Matlab Script node running fast enough to run at a time of 6ms. Also no way it works in a deterministic way at all. He needs to communicate with an external program, so its execution time is really unlimited.

Maybe you are looking for

-

My MBA 250 boot drive is full. I'm looking for suggestions how to find, review and remove effectively large files, so I can make a real dent in the problem. Thank you.

-

Add radio station to a playlist?

I have an older versions of iTunes radio playlist. I want to add a station to the list of internet stations iTunes. I can't do the sidebar while I put station highlighted to drag in the display list. I can't copy and paste into the playlist. Why is i

-

Request OEM licensed copy of Windows 7

Hello I have a desktop with pre-installed Windows 7. I would like to do a new installation on a new HARD drive but I don't have Win7 installation disc. How can I request an ISO? I read this post https://forums.lenovo.com/t5/Windows-7-Discussion/Windo

-

HOLA me hace falta saber como crear una simple ventana in labview as fair application para despues cerrarla, sea como una bienvenida para mi

-

Hi HP'ers. I had to do a complete reset (Menu Engineering, no Semi-, partial reset) to get my Officejet 6700 Premium working again. As you know that a reset complete a little more to return to the factory settings. I wonder now, if a complete Reset a