Zoom fft fpga

Hello world

I have some general questions about FFT on FPGA and the resolution of frequency spectral analysis.

To establish understanding:

I want to read the frequency with fs = 500kS on my FPGA. The FFT of the FPGA palette function allows a maximum of N = 8192 samples. This results in a resolution of frequency of fs/N = 500,000/8192 = 61 035 Hz and a bandwidth of fs/2 = 250 000 Hz.

My destination in spectral analysis is a resolution of 1 Hz in the range of 9 kHz to 11kHz.

My questions:

1. is there a similar function for FPGA as the 'Zoom' FFT applications in Sound and Vibration toolkit or can I use it on the FPGA target-VI?

2. is there a code for another example ' overlap and add ' or ' overlap and save "-method for the Fourier Transformations on FPGA?

3. any other suggestions for the problem described?

Best regards and

Thanks in advance

Sow

Hello Scott,

The result of your calculation is correct, you get a frequency of 60 Hz about resolution, but how you calculated it is false. If you sample with 500kS/s you can have a maximum of 250 kHz and FFT frequency you'll 8192 lines in your spectrum, so theoretical, you would have a resolution of about 30 Hz. But the FFT on the FPGA is both sides, that is, it returns the positiv and negativ frequencies. You cannot use the negaive ones, so you have only 4096 lines left from where you get a frequency of 60 Hz resolution about.

That being said there is no Zoom FFT for FPGA and you cannot use the Express VI of sound & Vibration TK here.

So, if you need the frequency upward to 11kHz, you could decimate the data and samples with 22Ks/s, then you get a 2.7 Hz resolution.

With a fixed block size you can get a better frequency resolution to measure a longer time.

Hope this helps,

Christian

Tags: NI Software

Similar Questions

-

Using FFT to palette spectrum Subvi Interface of FPGA functions

Hello

I use the card PCI-5640R and PXI-5600. I want to use the "scale" and "FFT" exspress screws to the range of functions 'Mathematical FPGA and analysis' in my VI "FPGA VI" and "FFT spectrum for '"FPGA interface"in my"host VI.

A poster of the code examples in which these three subVIs are used can.

Thanks in advance.

Kind regards

Rashid

Hi rachid,.

There are two examples of delivery here: LabVIEW 2009\examples\R Series\FPGA Fundamentals\Analysis and Control\FFT\

Jim

-

Exhibitor block signal - Xilinx FFT v7.1 - FlexRIO - FPGA

I use Xilinx FFT v7.1 IP (FPGA - OR 7965R, LabVIEW 2012). I am computing the FFT of real integer 16 bit signed.

Bit 5 signal exposing block block floating point FFT in module v7.1 Xilinx FFT signed or unsigned? Pdf document talks shift to the right of the data output to use the dynamic range, mentions not moving to the left, neither gives sufficient detail on this subject.

Is there a base value as format IEEE floating point should I use to find the correct output value?

I guess that it is unsigned unless you have comments to the contrary. The basic behavior is to keep bits on the left in order to prevent any overflow, so the scale always implies move on to when you think that some of the more significant bits are unused. They provide an example of b00101 = 5, so that indicates there is no bias to apply.

-

FFT on several channels in FPGA

I have a client with a 9076 (Spartan-6 LX45) who wishes to perform the FFT on several channels of a module of 9205.

I never run FFT on several channels and never run out of space on the FPGA before, but I strongly suspect that this could change that. Before I start to code this and play, someone can experience with this scenario - that offer you an optimal architecture / let me know how many channels can I expect to treat?

Hey Jed,.

As someone who has done a very similar application, but with the DC/RMS measurements, I can say with confidence that Yes, this is going to change that... How many channels your client wants to do and what kind of flow? I was able to get up to 64 is going, but it took most all of the fabric, and I had to write my own calculation of DC/RMS multiplex VI. So under a flow of course (I think we had each channel was updated to 1 Hz with 1000 samples per channel). Therefore, when writing a VI that multiplexes across all channel data, you could theoretically get many channels out there, but you sacrifice a flow.

Basically, I modified the existing Express VI to store its State in BRAM between each call and he's travelled to the number of channels * samples I was doing. Not terribly difficult, but your time trying to find a good balance for the given application.

-

Should I reset the FPGA FFT when changing the input signal?

Hello

I have an application based FlexRIO where I do FFT on several incoming signals. The signals will be ranked so that I get first for example 4096 samples of Ch1 and Ch2 4096 samples, etc. This means that I don't have to do it in parallel of the FFT and I would like to reuse the implementation of FFT and windowing to reduce the use of resources.

I intend using the VI Express followed by the Express VI of FFT window scaling

http://zone.NI.com/reference/en-XX/help/371599J-01/lvfpga/fpga_scaled_window/

http://zone.NI.com/reference/en-XX/help/371599J-01/lvfpga/fpga_fft/

and I'll use them inside a SCTL.

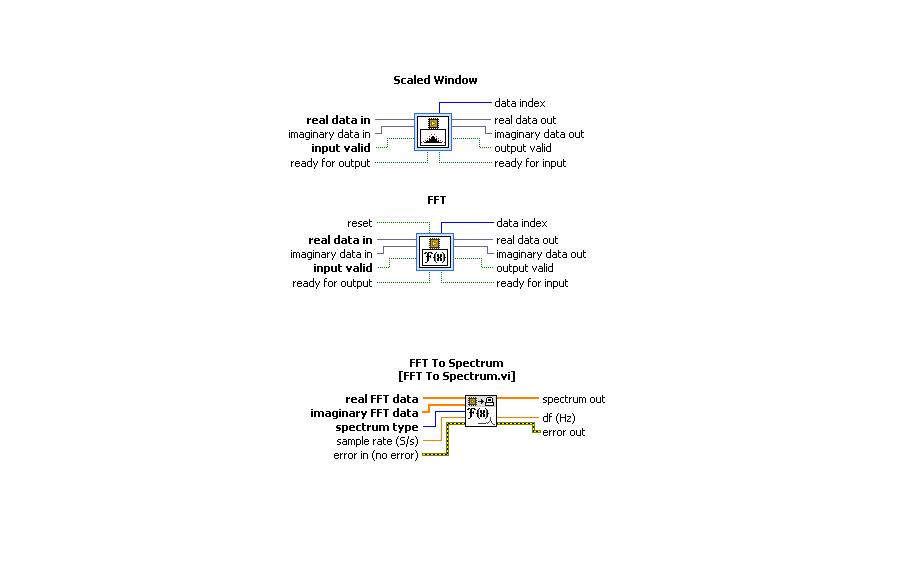

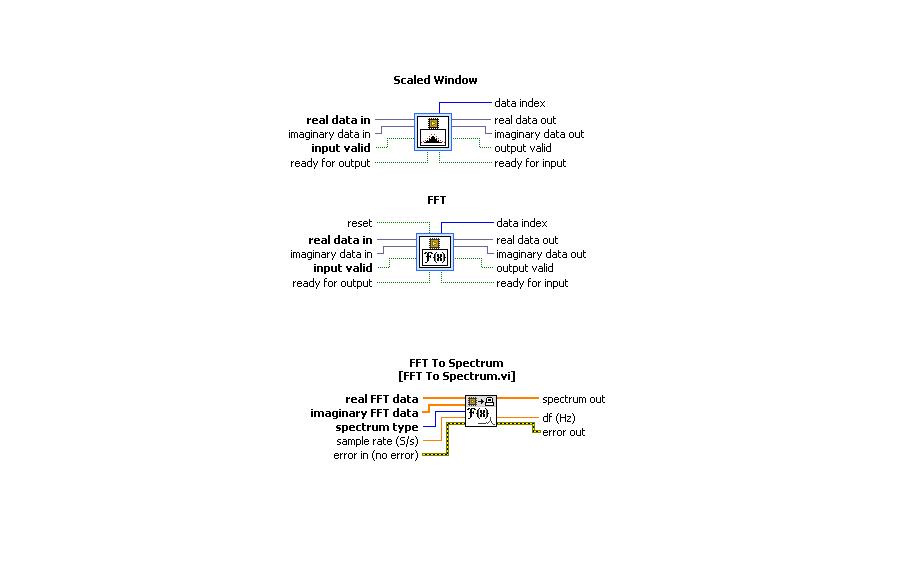

This figure comes from the section using the FFT and help illustrate the issue:

There is a discount to zero terminal for the fenestration and the FFT VI.

Are there internal registers in the windowing and FFT which force the image 1, image 2,... from the same signal or is it possible for the first entry in a framework of Ch1, the next frame belonging to Ch2, Ch3 gaze and so on and always get reliable results?

Another way to ask the same question: if I have to reset the window and FFT when changing the input signal?

Thank you

Anders

Hi Cyphish,

When using the FFT of the LabVIEW FPGA vi express and windows nationwide express vi calculations are make it point by point so there will be no problem when going through different types of measures. Therefore, you should have no problem with your application.

Best regards

Menelaos.K

-

Using the Interface of FPGA functions palette

Hello

I use the card PCI-5640R and PXI-5600. I want to use the "scale" and "FFT" exspress screws to the range of functions 'Mathematical FPGA and analysis' in my VI "FPGA VI" and "FFT spectrum for '"FPGA interface"in my"host VI.

A poster of the code examples in which these three subVIs are used can.

Thanks in advance.

Kind regards

Rashid

The answer to this question is available to

-

I should probably Preface that I'm new to LabView and LabView FPGA news especially, so with a bit of luck, it's an easy thing that I am simply on.

I wanted to start with a "simple example" of an FFT on the work of FPGA. It seems to me that the simplest approach is to use the sample project 'Simple NOR-USRP Streaming' and my NO-2942R. This program distributes the antenna RF data, converts baseband and publishes these (decimated) data to the host, which then makes the FFT.

It all works very well.

But I want to spend the FFT for side FPGA of things, and that's where I meet trouble.

I found this (http://www.ni.com/white-paper/7088/en/) and I do not see any problem with my design, except that when I switch to the FFT, I don't see what 0 instead of data, yet apparently from rear switch works great. The problem is that if I have this example to read the data on the side of RF, and there are examples regarding using the FFT, I always get the same result (all 0) when I try to combind the two pieces.

I enclose my VI block diagram. Note all my Special of changes with the FFT, the FIFO in two and pass assistance or bypassing the FFT. Everything else is in the code example.

Thanks for your help!

Had, apparently I missed the connection "Ready for the entry" on the bottom of FFT block. Threw me because he 'built' without it!

Thanks for this example, IronBrotha. While it has not helped with THIS specific problem, it gives me some ideas for my next step which is VERY similar to this example.

With regard to the VI, sorry to hear that it was not complete. I assumed that since I did not add any void live in an example of a default that would work only... but clearly I need to view the file integer lvproj in the future.

-

Error 50400 FlexRIO example "Coprocessor FFT"

As the title says, I have tried to run the example "FFT co-processor" located in LabVIEW 2013 FlexRIO PXI-7954R FPGA with examples but kept "ERROR-50400 occurred to the Invoke method: FIFO.» Write in TNI .vi co-processor (host). Possible reasons: the transfer has not completed within the time or in the specific number of retries. ».

I use LabVIEW 2013 SP1 with Xilinx 14.4 of the compiler. I didn't modify the code except copied the FPGA vi to the PXI-7954R target newly added and recompiled; and change the FPGA VI reference in the host vi as a result.

I tested the code in simulation mode (i.e., run VI FPGA on development with simulated IO computer) and it worked fine. However, when running on the target FPGA it does not work. I followed the 'empty remaining items' on "host-to - FPGA.Write" at the host vi and the value was 5. And "other" in "FPGA-to - Host.Read" in the host vi is 0.

It has something to do with the FIFO buffer size? Suggestions or comments are greatly appreciated.

Thank you

Bing

Theres a race condition in the code of the host. If you try to read before you write, then the FIFO is to expire. If you make sure that you write before you read while the timeout never occurs.

Attached is a version of the host code that writes then reads using a state machine.

-

SCTL FPGA flow and ready for input management

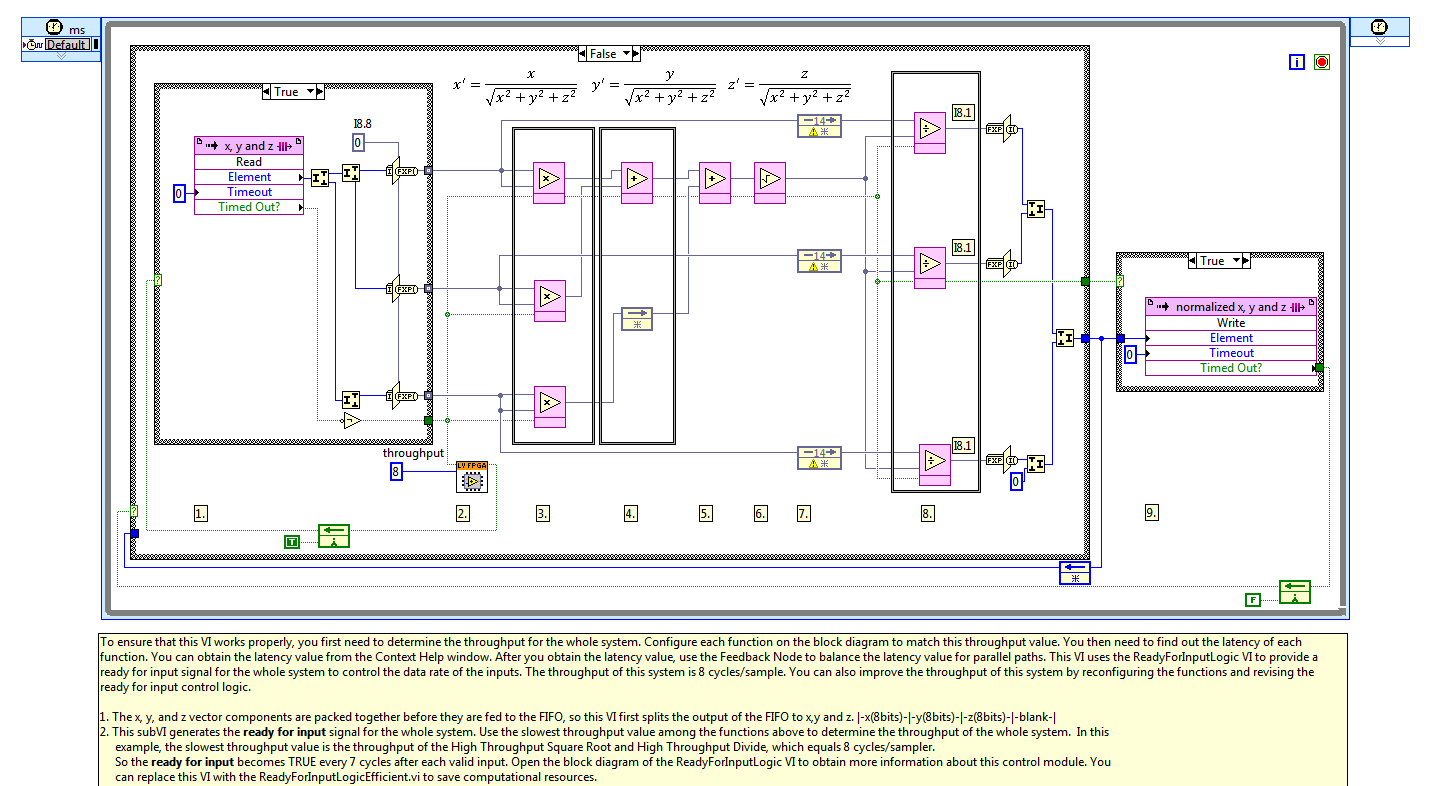

I studied the FPGA Normalize vector LV examples and I have a question on the loan for wire entry (see the attachment for the diagram).

A Subvi (named ReadyForInputLogic) is used to generate a ready for the true input signal each 7 cycles after each valid entry.

I understand the purpose of this sub - VI but it's the Subvi can be replaced by a wire between the 'ready for the entry' exit last ditch block and case diagram where the FIFO is read?

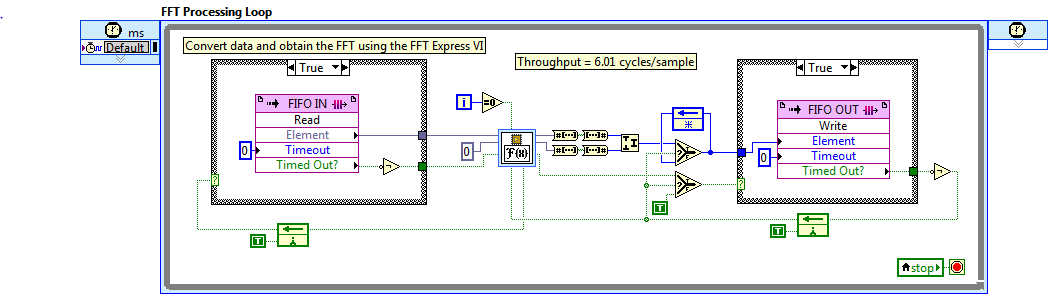

I also studied the example of co-processing FFT and there is no need to use this kind oh Subvi:

I modified this example to add some multiply and divide blocks after the block of the FFT. Thus, the flow of any new is increased to 8 cycles/sample (the block of the FFT is not the bottleneck).

I have to add the ReadyForInputLogic.vi in my SCTL Subvi read FIFO each 8 cycles?

Thanks a lot for any explanation

Zoomzoomzoom wrote:

RUFNEK wrote:

I understand the purpose of this sub - VI but it's the Subvi can be replaced by a wire between the 'ready for the entry' exit last ditch block and case diagram where the FIFO is read?

Yes you can, but then you run the risk of dropping a result when writing to the FIFO fails, because it is full. The logic is currently configured to stop processing vectors until the FIFO is not full.

RUFNEK wrote:

I modified this example to add some multiply and divide blocks after the block of the FFT. Thus, the flow of any new is increased to 8 cycles/sample (the block of the FFT is not the bottleneck).

I have to add the ReadyForInputLogic.vi in my SCTL Subvi read FIFO each 8 cycles?

Thanks a lot for any explanation

You must add the latencies to determine how many times you can read FIFO. The FFT under Setup for this example has a latency of > 5600 cycles before the output is valid. -

Xilinx FFT IP 7.1 (equivalent of 4-wire Handshaking)

Hi all

I'm trying to figure out how to get the IP of 7.1 Xilinx FFT to handshake properly as the 4-wire LabVIEW FPGA FFT Express VI. I need the use of Xilinx FFT because of the constraint of maximum length 8192 on vi express.

The common 4-wire for the handshake are:

ENTRY: entry valid

ENTRY: ready for the output

EXIT: exit valid

RELEASED: ready for the entrance

The Xilinx includes a few pins that are similar such as

OUTPUT: valid data

RELEASED: ready for data

OUTPUT: fact/edoné

ENTRY: Activate the clock?

Any ideas on the pins, I can use as INPUTS: input valid and ready for printing?

Thanks a bunch

Hi Jeffrey,.

I have attached an image I hope you find it useful.

Valid entry will match the activation (EC) clock pin

Output valid with valid data (dv) and

ready for the entrance with ready for data (rfd)

Let us know if you have any other questions.

Thank you

-

Help with fft vibrations without using the package of noise and vibrations

I'm looking for help in the analysis of vibrations. I use an example updated NI 9233 VI, to get a signal from the accelerometer for display using a FFT power spectrum. I'm not entirely sure if it works, because it's the first time I've ever done vibration analysis on LabView. So if you could explain a thing or two about vibrations or TFF, I'd be more than willing to hear from you. I have included my code along with a photo of an analysis of vibration of the computer, I work with. (even when I don't know if his work that I just thought it would be good to show an output)

Brandon

Data sheet:

I have LabView 2011

I FPGA, real-time

I have a model of research of Wilcoxon accelerometer 797-33

With an NI 9233

On a cRio-9012

Hi Brandon,.

You can use the FFT Complex (photo attached) to calculate the magnitude of the acceleration at different frequencies. You will need to take a little further to build a new waveform with this release, which includes d0, df and the output of the FFT. In order to calculate the df, please refer to the user manual on page 10-3. With respect to the scale that is output by the FFT, it must be same as input. Hope this helps to answer your questions. Thank you!

See you soon,.

CARISA Leal

-

FPGA graphic wavefrom does not

Compact rio using a fpga. 9014/9114

In a project of interface fpga if I create table and then plug it directly into a waveform chart it says that the table must be of fixed size.

However, I tested using a constant arrary of fixed size, initialize arrary to size fixed... etc, but it always happens with this error when you try to run the VI.

I have autopreallocate tables and strings as stated in the help file, but still it comes up with the error.

LabVIEW 11, sp1 (completely up to date)

I am running as a 'run on the development computer.

The arrary is fixed point type 27 bits wide (fft output)

First of all, in your code, you use a graphicof the waveform, not a graphic waveform as what you wrote in your messages before!

Then DBL is currently a data type not supported on the platform FPGA LV. There is also a strange problem with graphics on their type has spread to the FXP data type.

So the question I have, is that if you place a waveform graph or a chart in the palette, it is DBL. If you then connect an array of FXP, you get the error message you see since the graph or table does not spread to the FXP data type. If you change the data type of the table for example I32, the type of charts or tables becomes I32. If you redefine the I32 with FXP then, everything works as it should.

This means for you, first create a table of I32 and connectivity for the chart or table to get rid of the wrong size fixed. Then change the table in FXP.

I just need to do some more research on this problem and will post backs.

Christian

-

The FPGA using mathematics and analysis of VI

When I'm programming on our FPGA (in one OR cRIO-9004) my code will not compile when I use the VI in the calculation tab and analyze FPGA. The code will stop compilation and just say idle in the status area.

I can't undewrstand it.

If someone could help me it would be great. I'm looking to perform FFT analysis on sgnals.

I discovered that it was because I was not logged as an administrator on the computer. Therefore, necessatry files could not be written.

Problem solved now so just a heads - if you see something similar

-

I have as part of the much bigger problem simply multiply the elements of the two tables and summarize the terms to give a single output constant.

There may be 100 terms mean in the table, but this test that I attach only uses 6 numbers and the same table twice for simplicity. I'm so calculate the scalar product of two vectors of surface where ' is transposed.

It has been suggested that I shared the calculation in two so that I have summarized the first 3, i.e. 0,1,2 and 3 last, IE the 3,4,5 in parallel (as in the program). Of course, I get the same end result. Would this double FPGA execution speed because it's doen in parallel?

The reason why I ask this question which is probably if I used a power of 2 amount of data I could divide it again and still a bit like a FFT,.

Does make sense? or is the FPGA "unpack" the loop FOR in any case is not worth?

the program displays the original and the split method.

Thank you

The side is an FPGA will give you gains of speed whenever you parallelize computation. The downside is that you still have to do most of it. No shipping FPGA course OR product made optimizations such as loop place (although the standard LabVIEW). This is a dangerous operation that could increase the size of the code and FPGA programmers tend to be picky about these things.

If you can get speed gains each time you parallelize, but you will have to do it manually. Note If your parallel loops that access a shared resource (memory, state variables, etc.), the claim on this resource will reduce the overall speed, so you get. Also, if you can integrate calculations in a single-cycle timed loop, you will get there, effectiveness as well.

Good luck and have fun!

-

I am trying to acquire data from a ni9222 located in the chassis-9014 9114, cRIO.

But for some reason, the output data type is used as a 24-bit fixed point number?

However the 9222 is module of the ADC 4 channels 16-bit 500ks/S.

I want to run the data via a fifo (target scoped) to power a 2 channel FFT module (coregen), which accepts fixed point 16-bit numbers.

I seem to be anyway to change or correct the accuracy.

I increased the fifo to 24 bits to try to work around the problem, but then I can't seem to massage the 16-bit required format (that it should have been originally)

All this in the area of the chassis/FPGA

In another section of my main FPGA vi, I 16 bits of the data of NI9215 quite happily was sent down a DMA FIFO for the time real cRIO and connected to a USB key without any strange problems.

PS are the example any screws available for the use of the FIFO coregen and the 7.1 FFT coregen?

I use the labview 11

In my view, that the data is being multiplied by a scale factor to convert the entry to volts instead of charges. I think it's so when you mix different modules with different resolutions of data acquisition, the outputs are in volts and can be compared, etc.. I know that I changed the properties of some modules for the former counties old-fashioned, but I don't remember exactly how I did it.

Bruce

Maybe you are looking for

-

I've owned as a slate-21 for a while and it is running Android 4.2.2 and supports the system is up-to-date. I just bought another and it is running Android 4.4.2. As far as I can tell the h/w is identical. So, how to make my old unit to the new versi

-

Friday morning I wasn't able to boot my computer more. When I start my computer it won't seek to set a parameter nr 3 of 3. And then it restarts again. My computer tried to install some windows update settings the day before with no success. I Don t

-

a box grey rectangular volume with a shown speaker and a red line through it, volume is on my desk. Nothing can be in front of her, and I see no way to get rid of him.

-

Help decipher files encrypted on XP

I use windows Xp and I am the administrator and the only user of the laptop. I have only my username and a guest account, has never been another account created or deleted. I have a small selection of folders containing photos videos and word documen

-

We had to reformat our computer and we had reinstalled everything everything went well past that we got on the interent fine, but when it came to the updates, we have just let it go, after the update retarted the computer, we've got a stop code 0x000